Method for realizing to reset main device in 12C bus and resetting apparatus and equipment thereof

A technology of reset device and implementation method, which is applied in the direction of instruments, electrical digital data processing, etc., can solve the problem of I2C bus being locked, and achieve the effect of low hardware cost and improved adaptability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

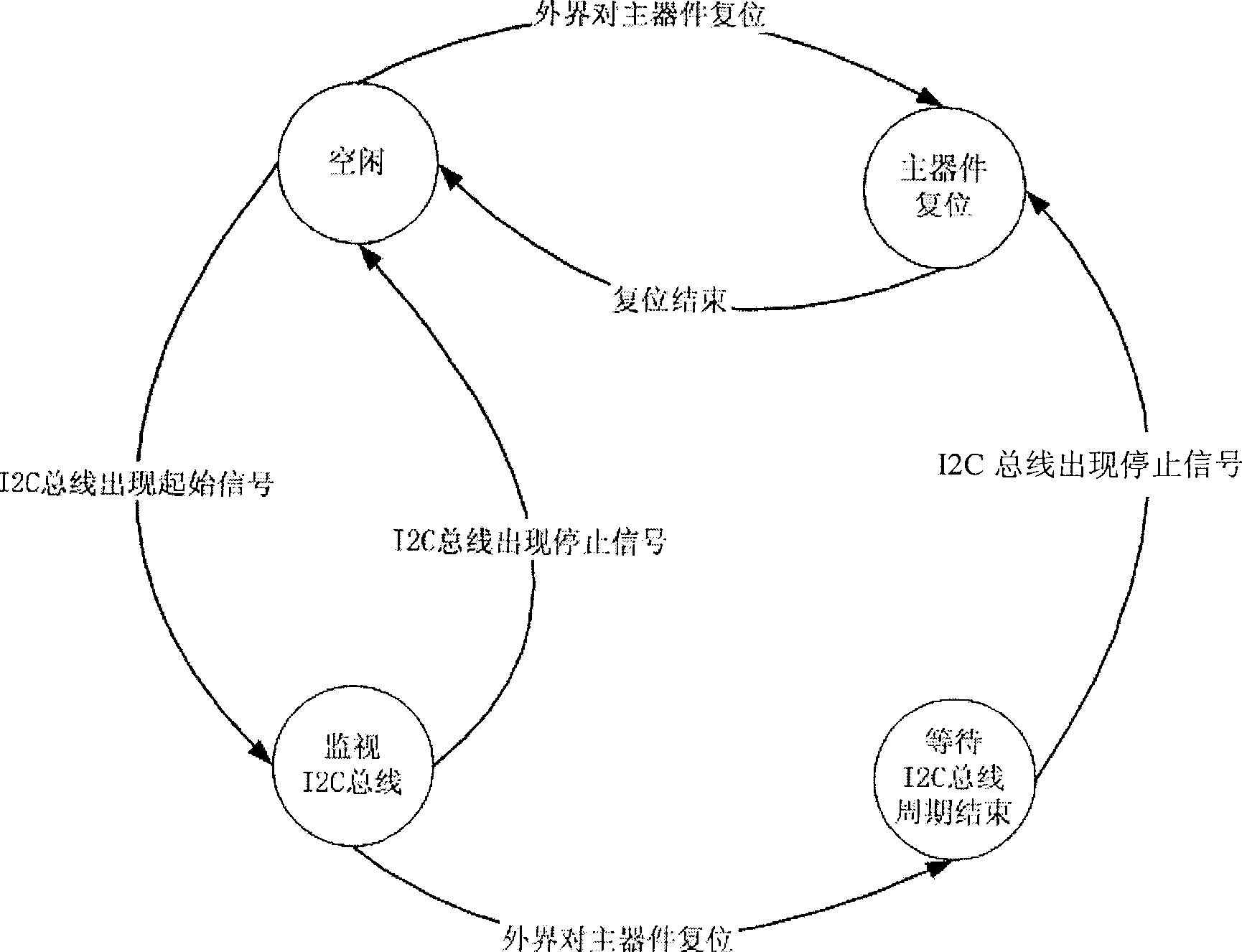

[0033] Below in conjunction with accompanying drawing, the implementation of technical scheme is described in further detail:

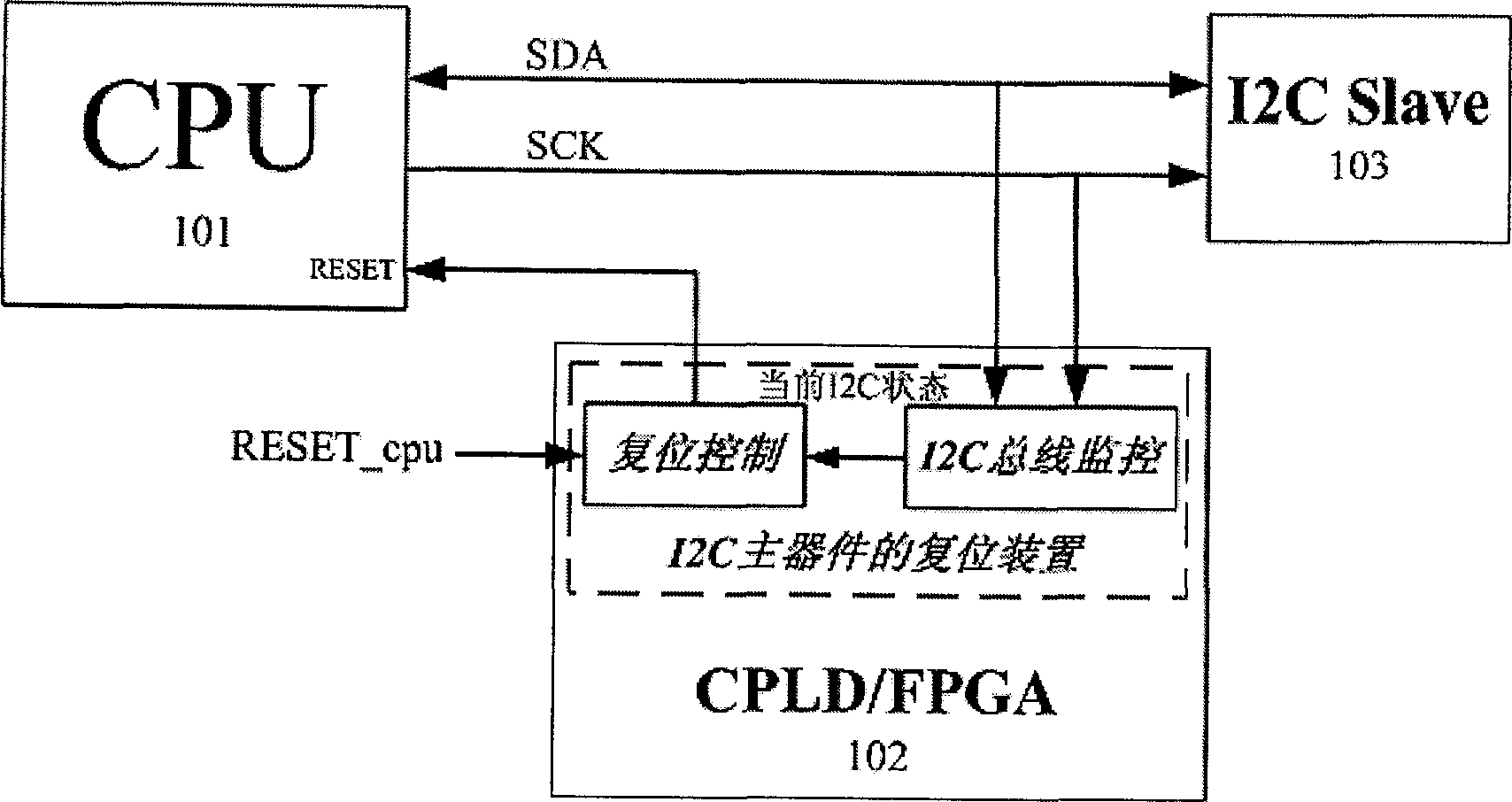

[0034] figure 1 Shown is a structural block diagram of the reset device of the master device in the I2C bus in this embodiment. As shown in the figure, the device includes a master device 101 on the I2C bus, a reset device 102 for the master device and a slave device 103 for the I2C bus. In this embodiment, the main device 101 is a CPU processor. Generally, there are multiple slave devices 103 on the I2C bus, only one of which is shown in the figure.

[0035] The reset device 102 is implemented by a programmable logic device (PLD) in this embodiment, and this device is a functional module formed by the internal logic circuit of the PLD. In practical application, in order to form modularization and adapt to PLD devices of multiple manufacturers, this functional module is generally implemented by hardware description language Verilog or VHDL to impro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com