Self-timed reliability and yield vehicle with gated data and clock

A technology for gating clock and data, applied in the direction of semiconductor device, electric solid state device, single semiconductor device testing, etc., can solve the problems of slow test, unreliable test, increase cycle, etc., and achieve the effect of improving production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

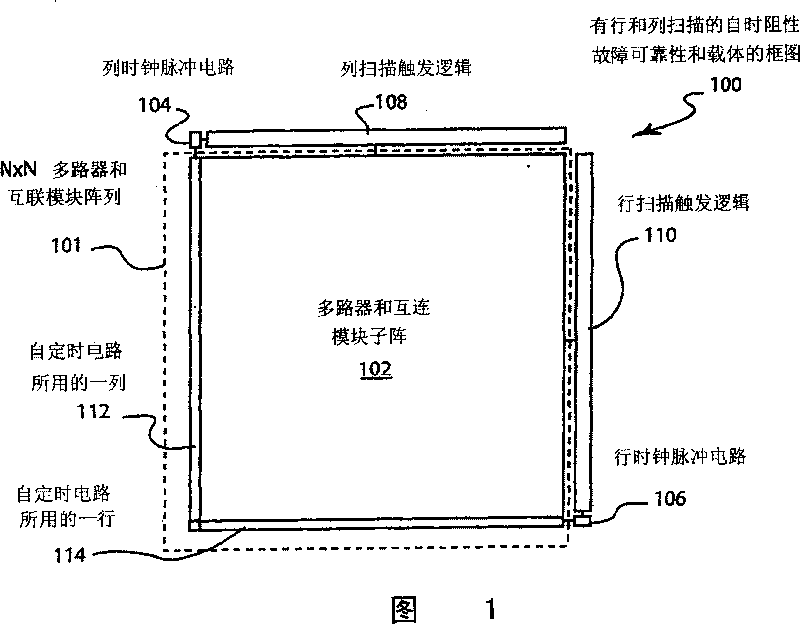

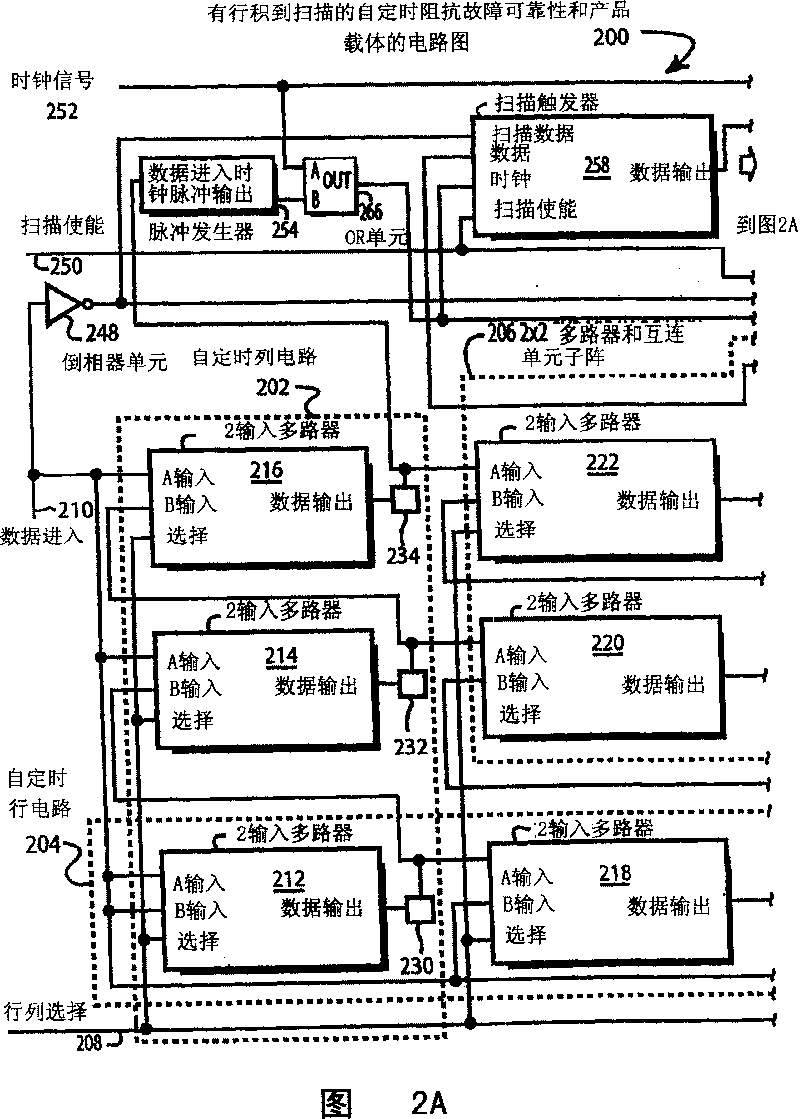

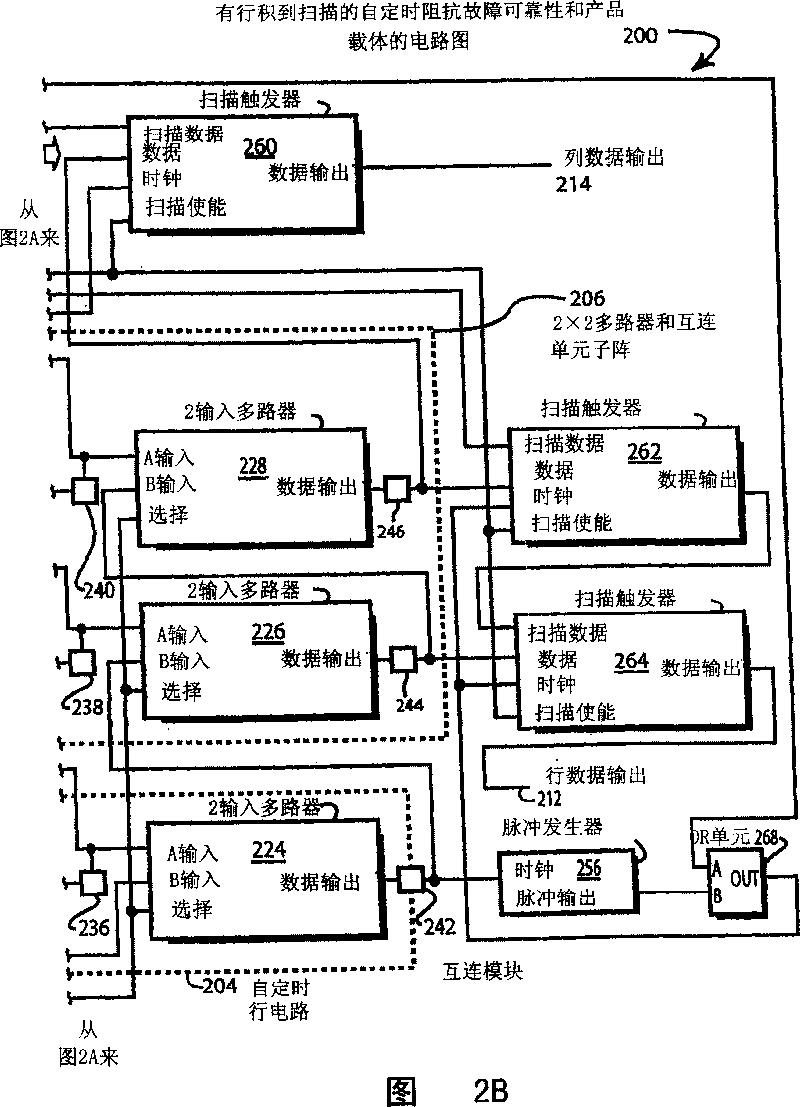

[0045] figure 1An embodiment 100 of a self-timed resistive fault test vehicle is shown in which integrated circuits are tested for resistive fault reliability and production and fault location is determined. Column clock circuit 104 receives signals from an NxN multiplexer (MUX) and a first column 112 of interconnect module 101 array. This first column serves as a self-timing circuit that takes a clock edge (usually from a lower speed clock signal) and generates pulses of a certain duration, which are then used to time the N× The speed of the N multiplexers and other columns within the interconnect subarray 101. The output of the other columns is loaded into the column scan trigger logic 108 using this timed pulse and the difference is registered. A signal registered at column scan trigger logic 108 other than the first column of self-timing circuit 112 indicates the presence of an irregularity, defect, or some kind of error in a particular column.

[0046] Similarly, row c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com