Pixel structure and mfg method therefor

A technology of pixel structure and manufacturing method, applied in static indicators and other directions, can solve the problems of load effect, different key dimensions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

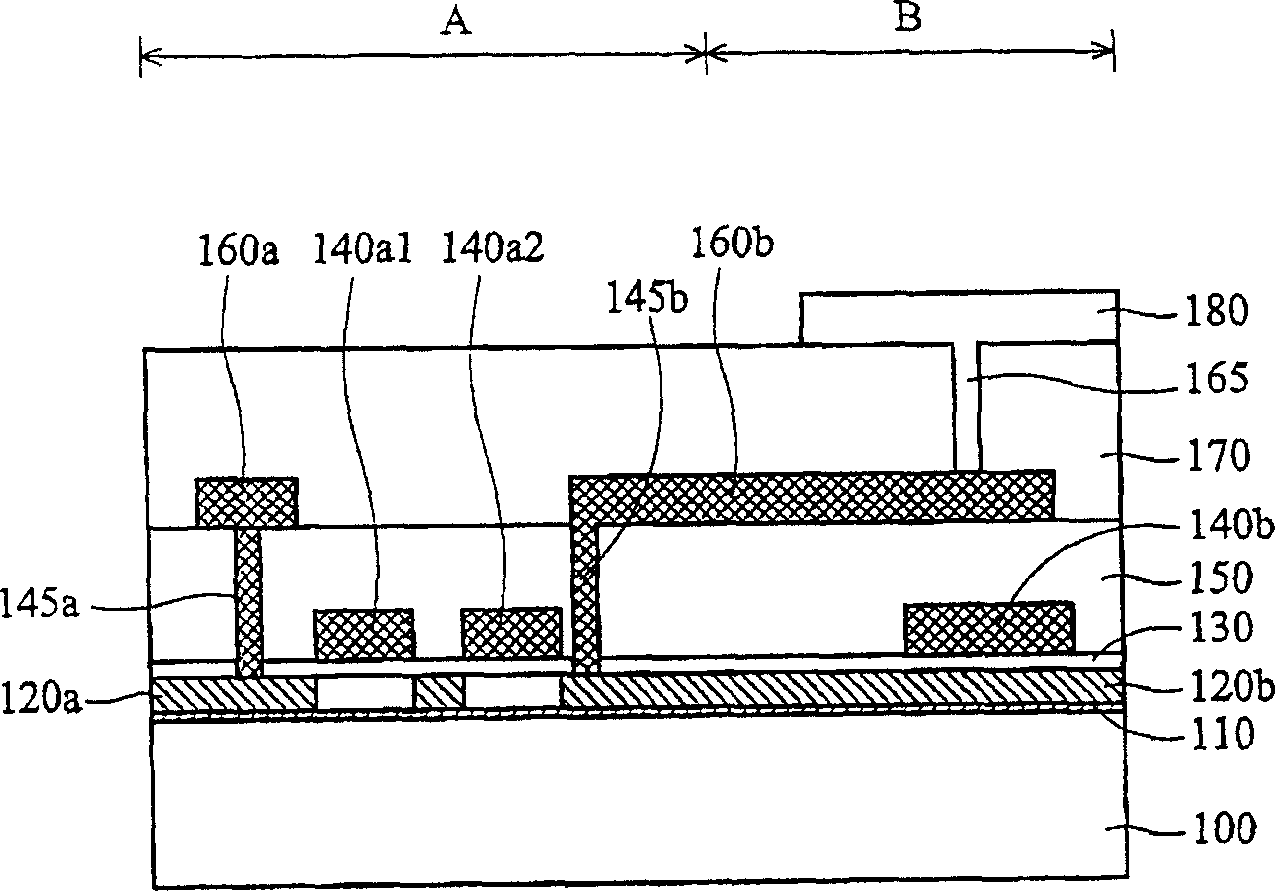

[0040] The following is a method for manufacturing a pixel structure according to the first embodiment of the present invention.

[0041] Figure 3A In order to show a cross-sectional schematic diagram of a patterned semiconductor layer formed on a substrate according to an embodiment of the present invention, it includes a thin film transistor (TFT) area A and a capacitor area B. First, the buffer layer 310 can be formed on the substrate 300 by means of chemical vapor deposition (CVD) or the like. The substrate 300 may include materials such as glass, and the buffer layer 310 may include materials such as silicon oxide and / or silicon nitride.

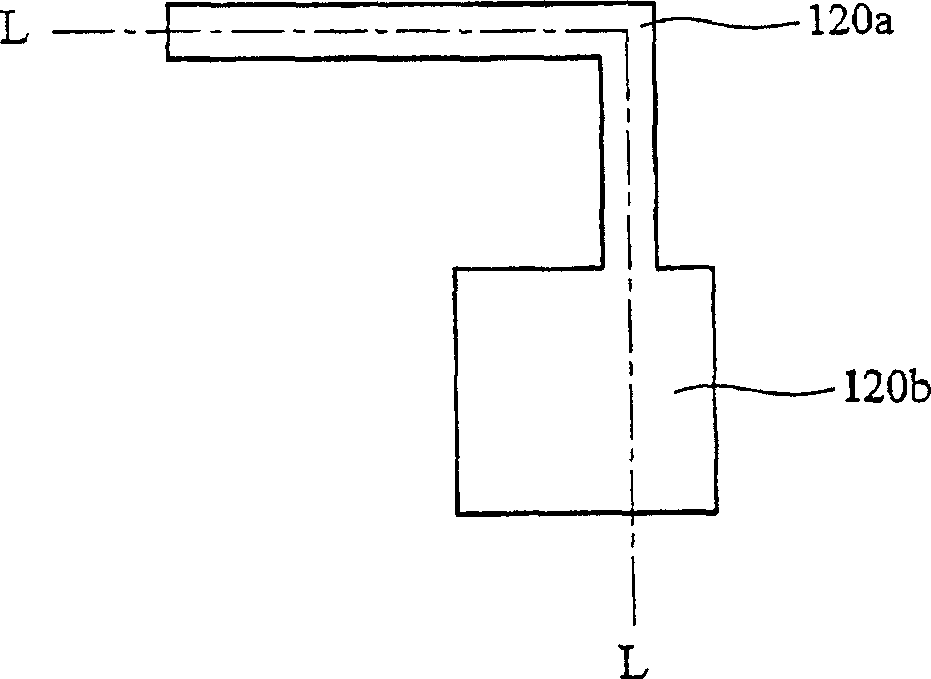

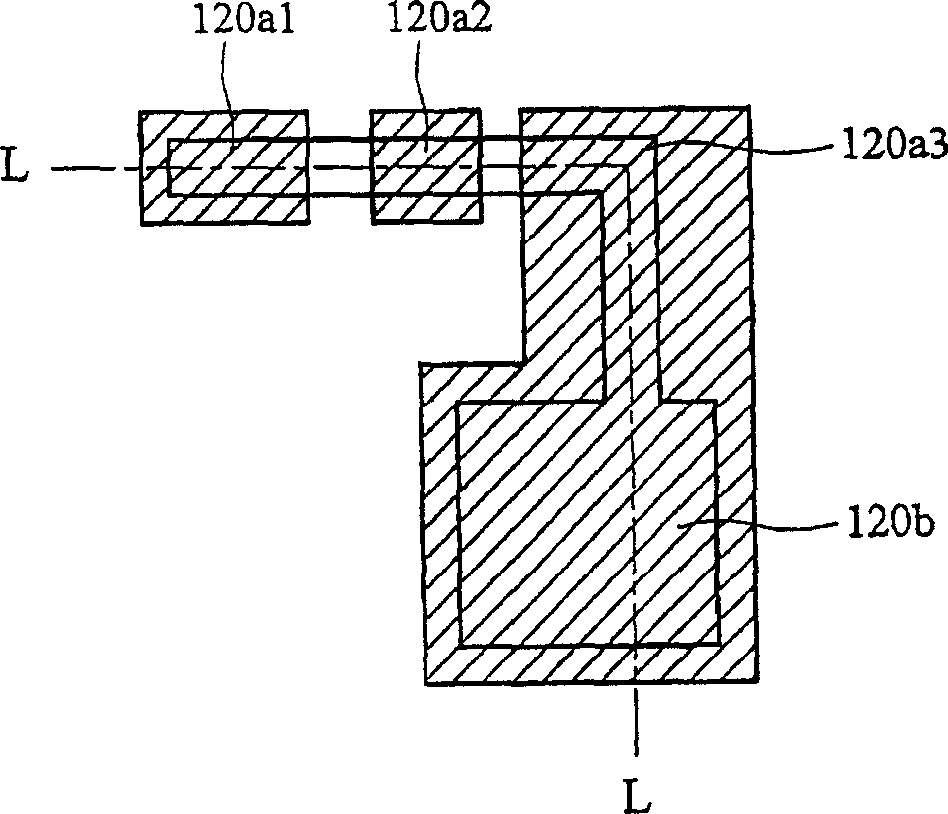

[0042] Next, a semiconductor layer is deposited on the buffer layer 310, and then a photolithography etching process is performed to form the active layer 320a, the bottom electrode 320b, and the opening 320c. The active layer 320a and the lower electrode 320b are not connected, and the opening 320c is used as the interval. The top view i...

no. 2 example

[0049] Figure 5A In order to show a cross-sectional schematic diagram of a patterned semiconductor layer formed on a substrate according to an embodiment of the present invention, it includes a thin film transistor (TFT) area A and a capacitor area B. First, the buffer layer 510 is formed on the substrate 500 by, for example, chemical vapor deposition (CVD) or the like. The substrate 500 may include materials such as glass, and the buffer layer 510 may include materials such as silicon oxide and / or silicon nitride.

[0050] Next, a semiconductor layer is deposited on the buffer layer 510, and then a photolithography etching process is performed to simultaneously form the active layer 520a, the bottom electrode 520b, and the opening 520c. The active layer 520a and the lower electrode 520b are not connected, and the opening 520c is used as the interval. The top view is as Figure 6A Shown along Figure 6A The section view of the middle section line L’L’ is Figure 5A . This struct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com