Semiconductor devices having different gate dielectrics and methods for manufacturing the same

一种栅极介质、半导体的技术,应用在半导体/固态器件制造、半导体器件、电固体器件等方向,达到阈值电压操作快速和可靠、减少负面影响、高速运行漏电流的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The invention will now be described in the form of several preferred but not limiting embodiments with reference to the accompanying drawings. It should be noted that the relative dimensions shown in the drawings are not to scale with the actual dimensions.

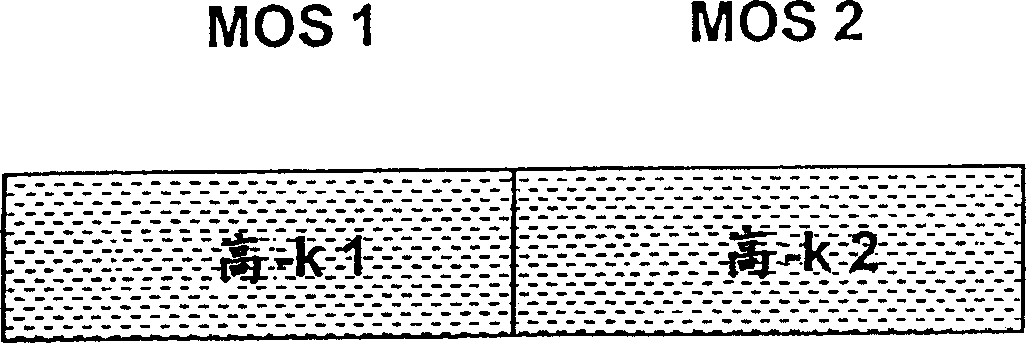

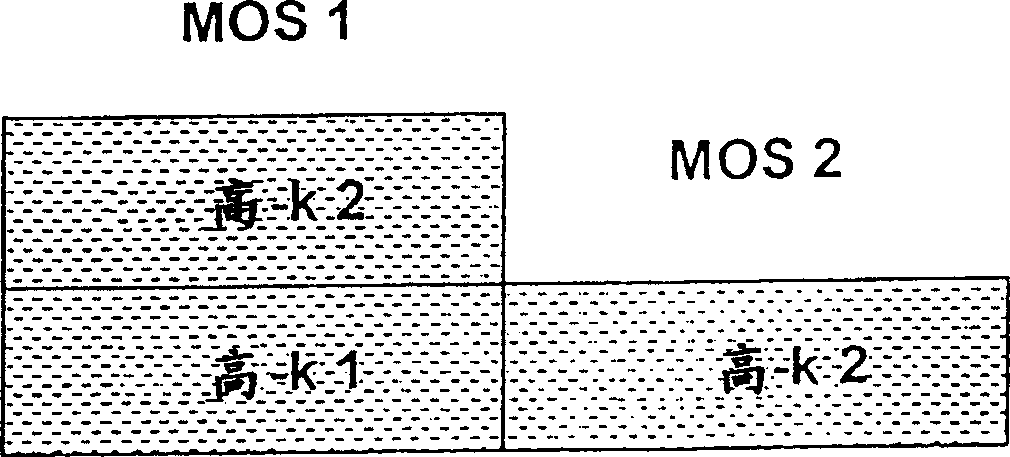

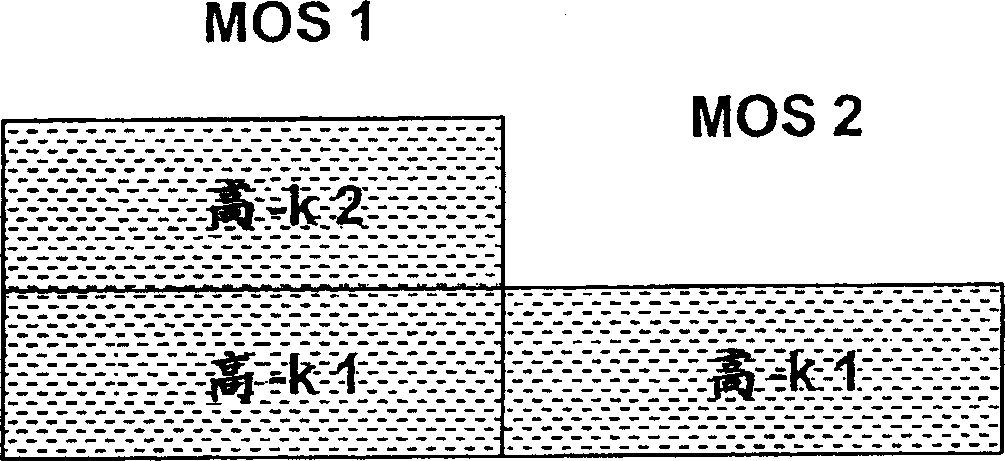

[0026] 1(A), 1(B) and 1(C) are simplified schematic diagrams of embodiments of gate dielectrics used in MOS devices according to the present invention.

[0027] FIG. 1(A) shows a gate dielectric of a semiconductor device including a first type metal oxide semiconductor (MOS1) and a second type metal oxide semiconductor device (MOS2). In some embodiments, MOS1 is an n-channel metal oxide semiconductor (NMOS) device, and MOS2 is a p-channel metal oxide semiconductor (PMOS) device. In other embodiments, MOS1 is a PMOS device, and MOS2 is an NMOS device. In the embodiment of FIG. 1(A), the gate dielectric of MOS1 is a first high-k dielectric material (high k1 ), and the gate dielectric of MOS2 is a second high-k diel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com