IP nuclear simulation confirmation platform based on PCI bus and proving method thereof

A PCI bus, simulation verification technology, applied to the PCI bus-based IP core simulation verification platform and its verification field, can solve problems such as difficulty in collecting test results, unfavorable real-time monitoring of the test process, difficulty in generating and controlling test signals, etc., to achieve design Reasonable, easy to use, and simple hardware structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

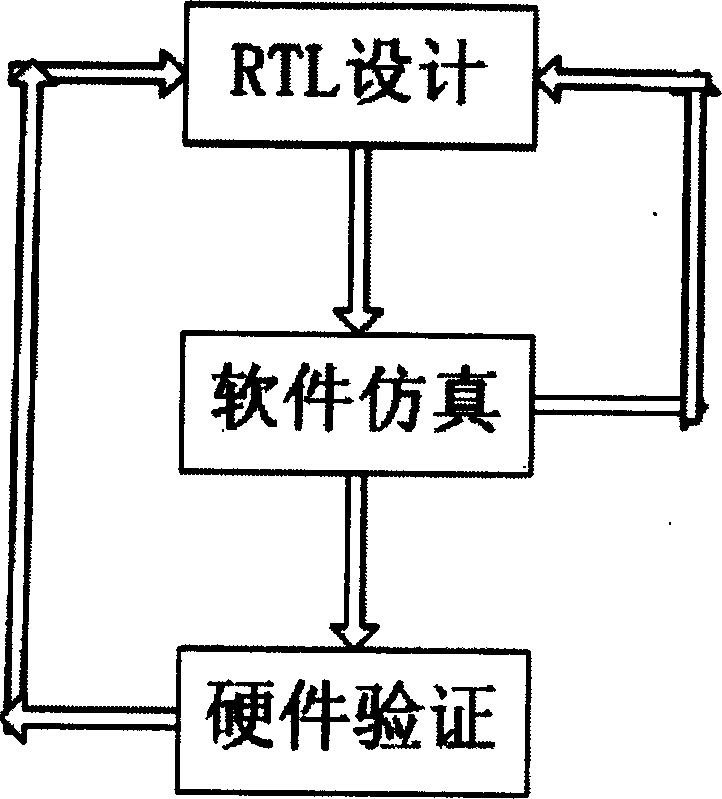

[0028] Such as figure 1 As shown, the verification method of the general soft IP core refers to the software simulation in the software environment to verify the correctness of the IP core function, and then write it into the FPGA device for hardware testing. If the test is correct, the IP core verification is completed. If there is a problem in the test, return to re-modify the IP core. The disadvantage of this method is: when performing hardware verification in FPGA, it is difficult to generate and control a large number of test signals for testing IP, not only difficult to collect test results, but also not conducive to real-time monitoring of the test process.

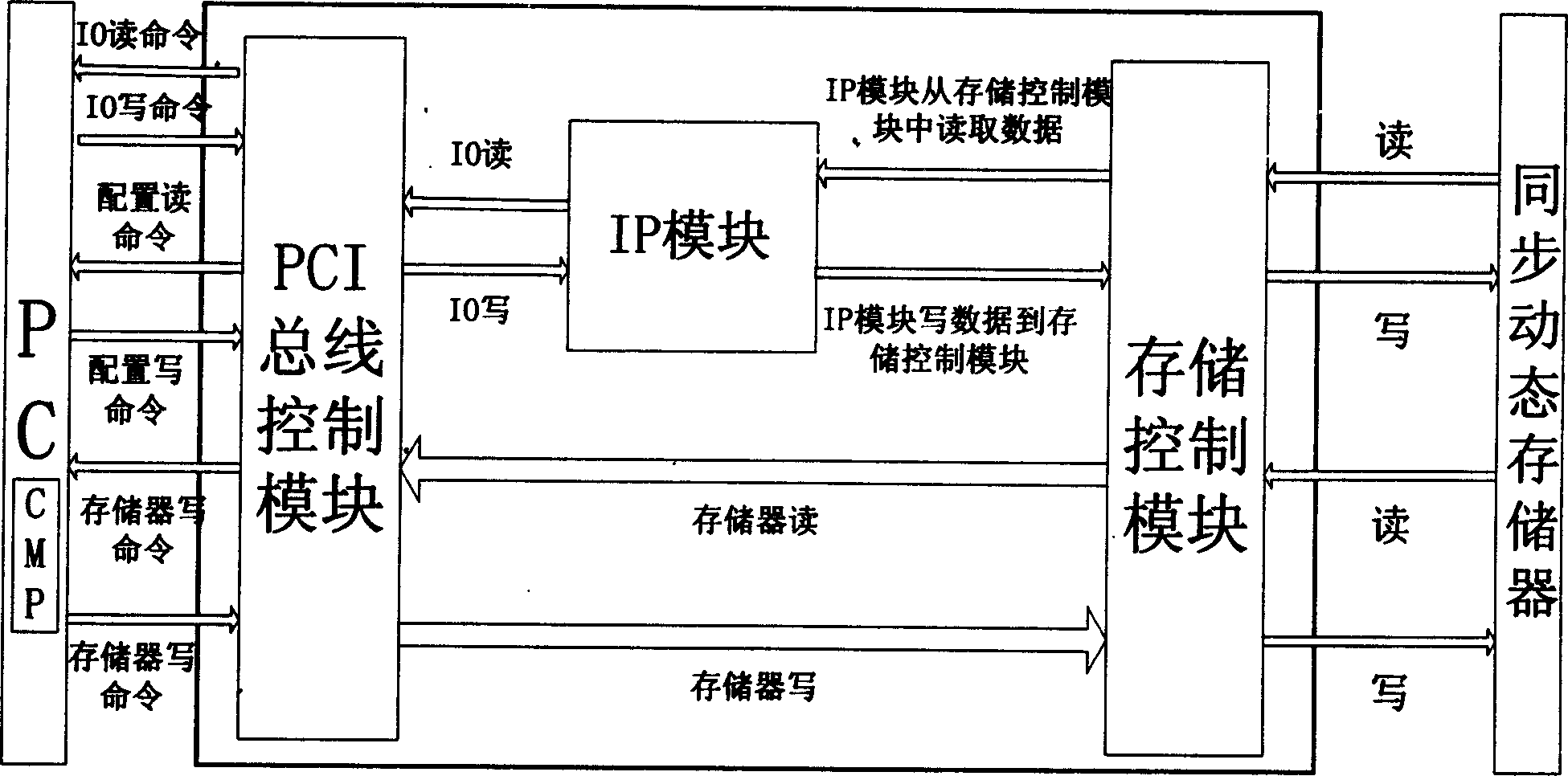

[0029] Such as figure 2 As shown, the PCI bus control module is a bridge module of the PCI bus, which is connected to the PCI slot of the computer and connected to the IP module...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com