Quick method for implementing noise optimization of integrated circuit supply network using decoupling capacitor

A power supply network and integrated circuit technology, applied in the field of RLC power line/ground line network noise optimization, can solve the problems of unsatisfactory optimization effect, inability to apply power supply/ground line network optimization work, and high algorithm time and space complexity, Achieve good optimization results, save running time, and reduce scale

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

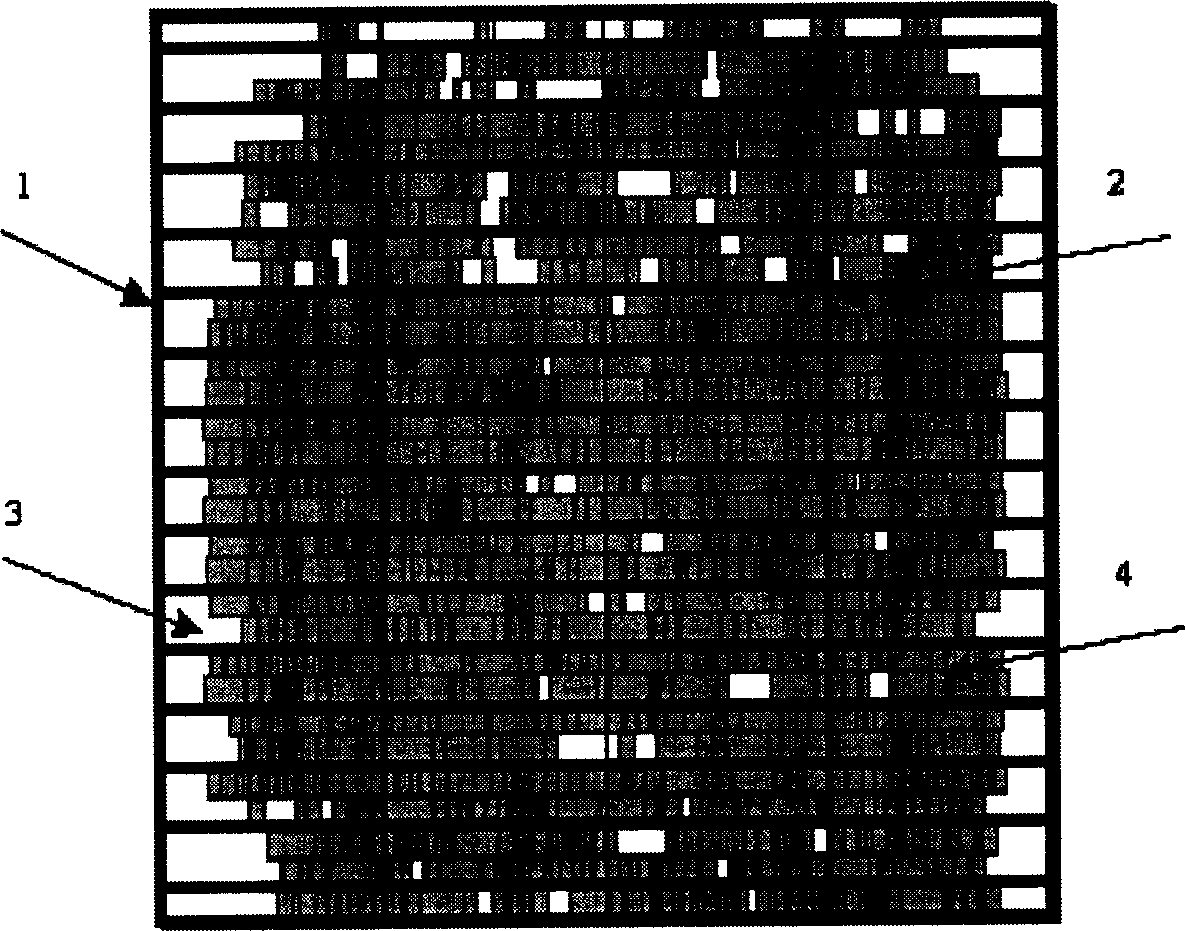

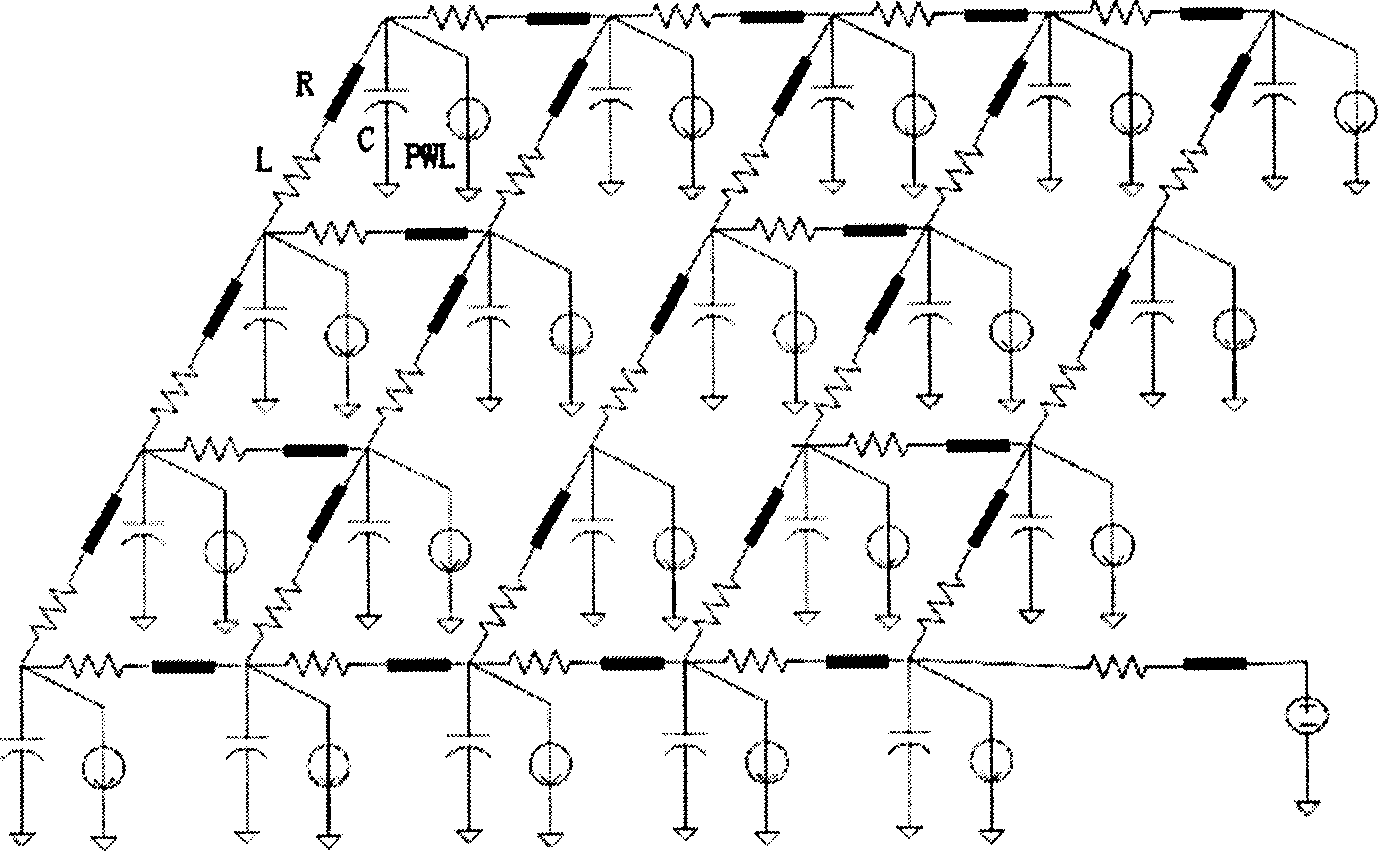

[0117] Use the def and 1ef format test circuit example u_cnt100 provided by the industry as an example combination Figure 8 The method of the present invention is used to optimize the addition of decoupling capacitors.

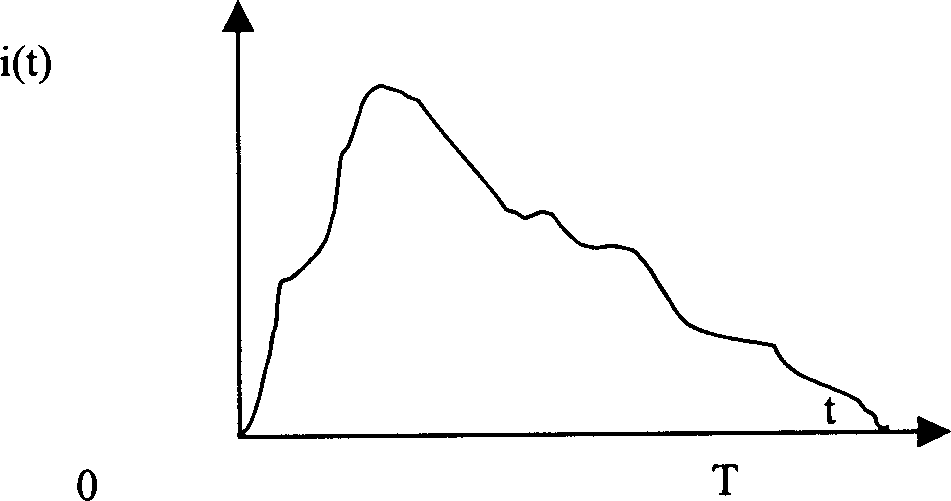

[0118] 1. Read in files - u_cnt100.lef containing library unit information, u_cnt100.def containing unit interconnection information, parameter file power.params and file current.dat containing sink current information. Establish the structure of the circuit according to the information read in;

[0119] 2. Transient analysis based on the equivalent circuit is carried out on the established power supply network, and the voltage waveforms of 806 nodes on the network are obtained;

[0120] 3. The result of transient analysis of this power supply network is that there are 91 violation points, such as Figure 10 As shown, the network needs to be optimized by adding decoupling capacitors;

[0121] 4. The voltage waveforms on the 744 leaf nodes are segmented and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com