Physic design method for analog and radio frequency integrated circuit

A radio frequency integrated circuit and physical design technology, applied in circuits, electrical digital data processing, computing, etc., can solve the problems that engineers are difficult to correctly give layout constraints, consume a lot of time, and slow automatic design, and achieve the most The effect of optimal wiring, small parasitic effect, and area optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be further described below in conjunction with the following non-limiting examples and accompanying drawings.

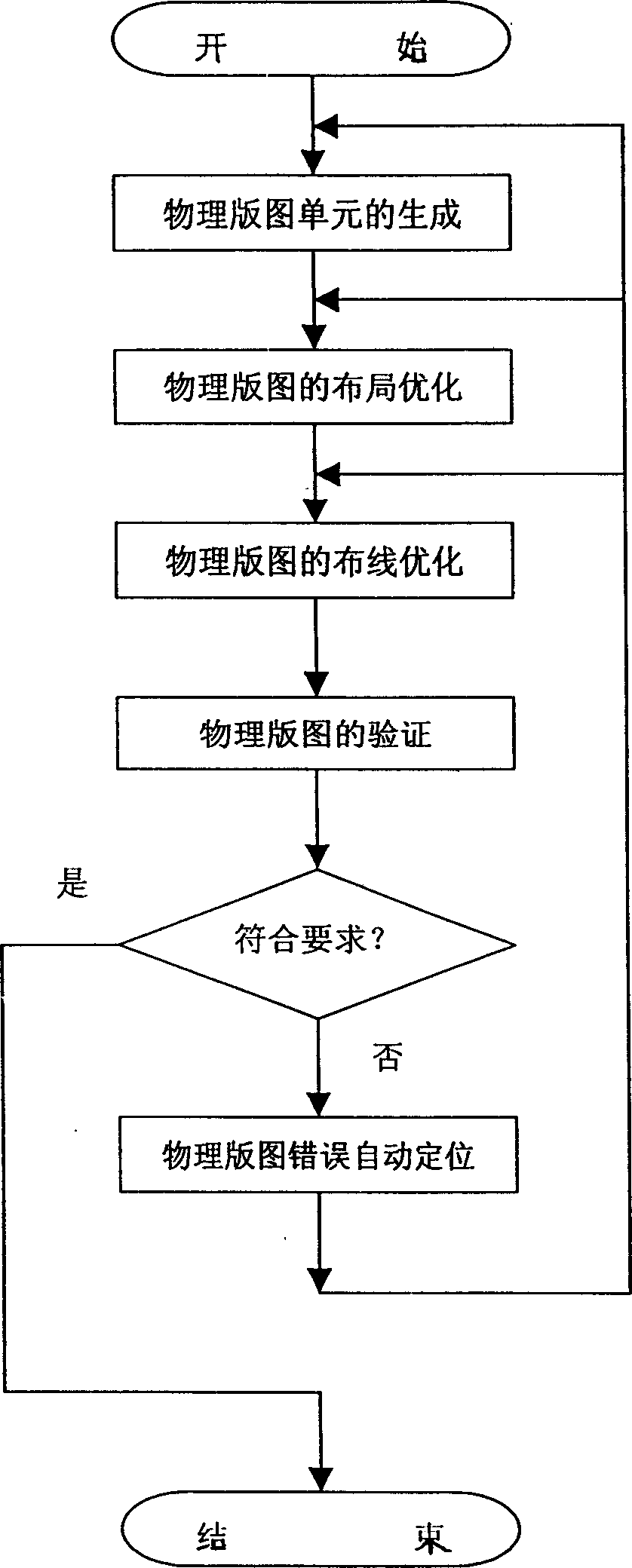

[0041] From figure 1 It can be seen that the steps of the physical design method of analog and radio frequency integrated circuits include: ① generation of physical layout cells, ② layout of physical layout, ③ routing of physical layout, ④ verification of physical layout, ⑤ automatic positioning of physical layout errors.

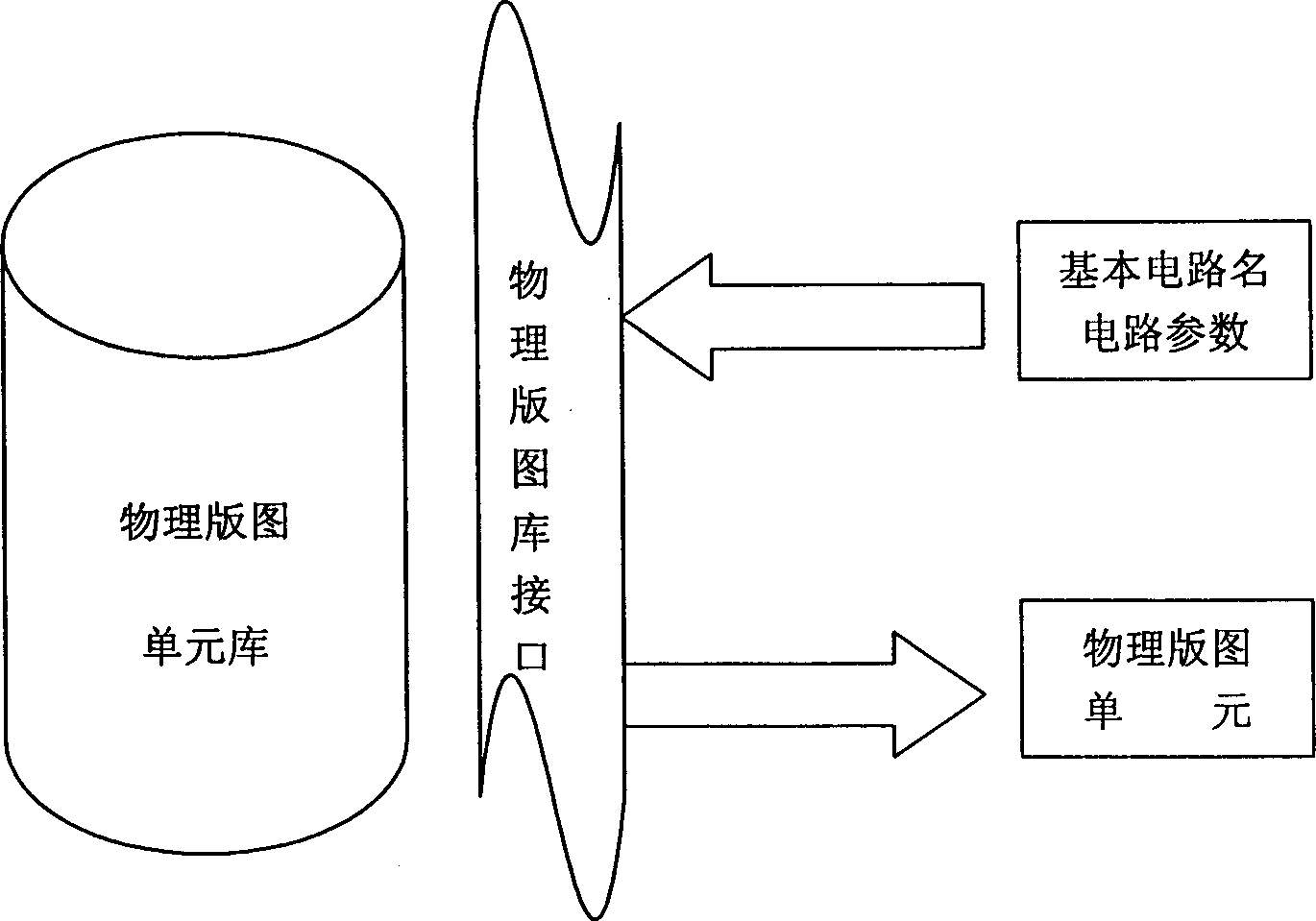

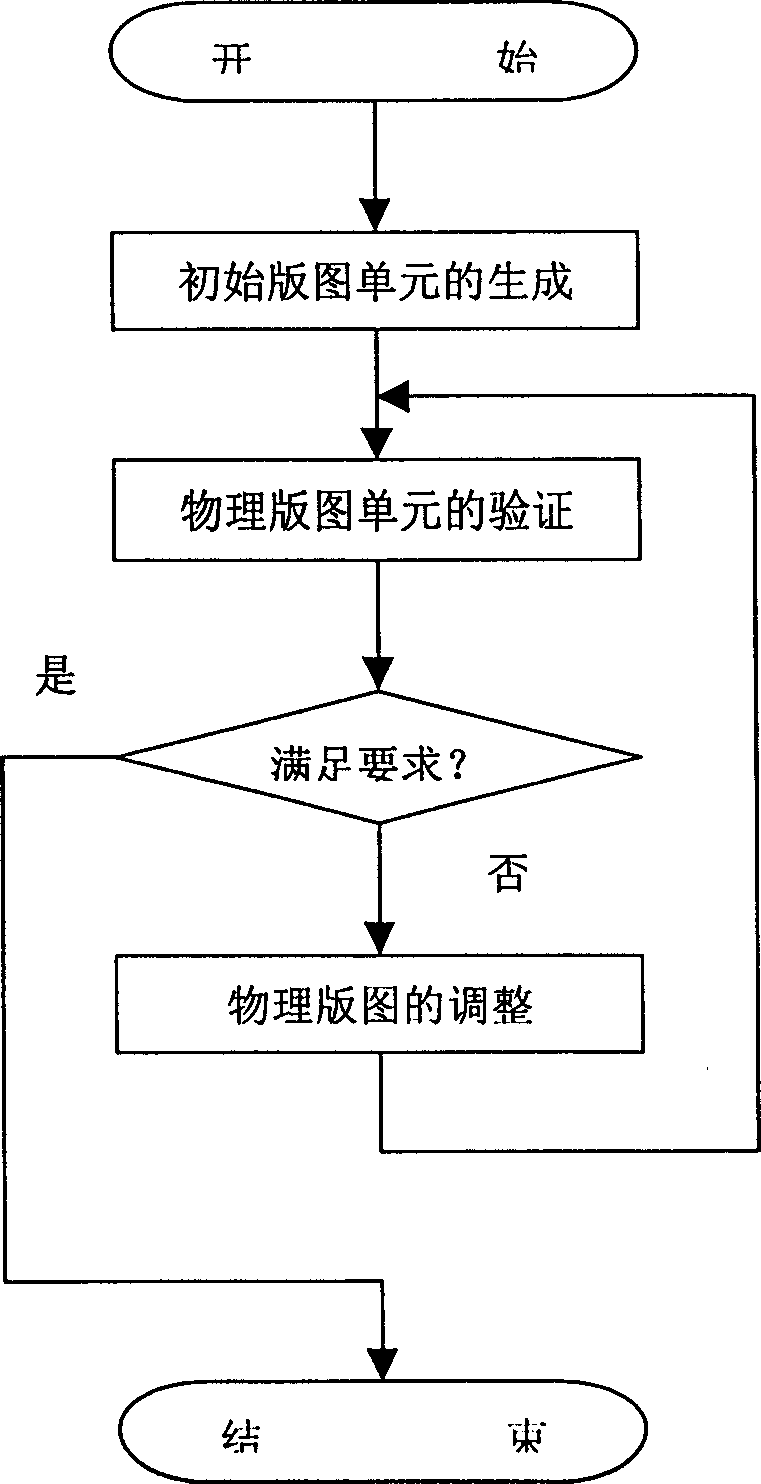

[0042] Among them, the step of step ① physical layout unit generation provides the necessary physical layout units for each unit circuit necessary for subsequent layout; the layout of step ② physical layout is mainly based on the layout requirements obtained by circuit analysis for the physical layout units provided earlier. Carry out accurate position placement; step ③ physical layout layout is mainly to connect the layout units with metal wires in the physical layout results provided above according to the layou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com