Memory element and its production method

A technology for storage elements and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., and can solve problems such as interface breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

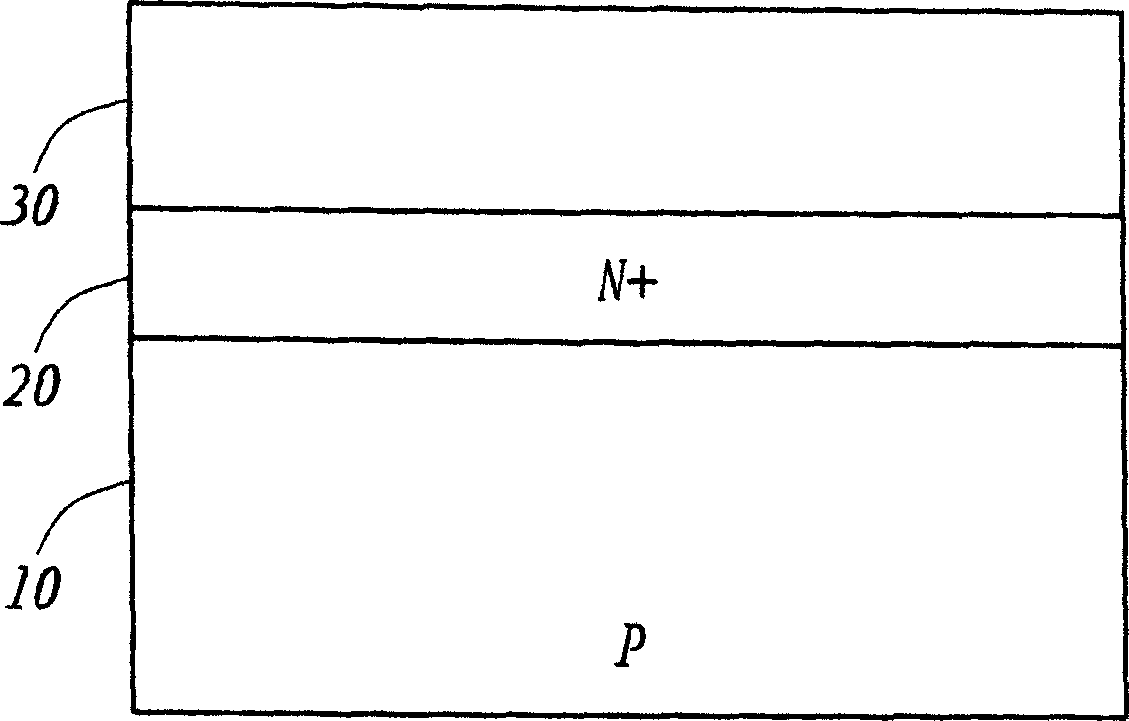

[0018] Please refer to Figure 1A ~ 1C , which shows a flowchart of a method of manufacturing a memory cell according to a preferred embodiment of the present invention. exist Figure 1A In, first, a semiconductor substrate 10 is defined, such as a p-type substrate. Next, a doped layer 20 is provided on the semiconductor substrate 10, and the doped layer 20 is used as a buried bit line of the memory cell. In one embodiment, the doped layer 20 can be doped with a large amount of n-type dopants (dopants), such as phosphorus, antimony or arsenic, and the electric energy and dose range during doping are about 35-150 keV ( kev) and 5×10 19 ~5×10 20 Atoms / square centimeter (atoms / cm 2 ), dopants can be introduced via ion implantation. After the doped layer 20 is formed, a dielectric layer 30 is deposited on the doped layer 20 with a thickness of about 200-600 nanometers (nm), and the dielectric layer 30 may be an oxide layer.

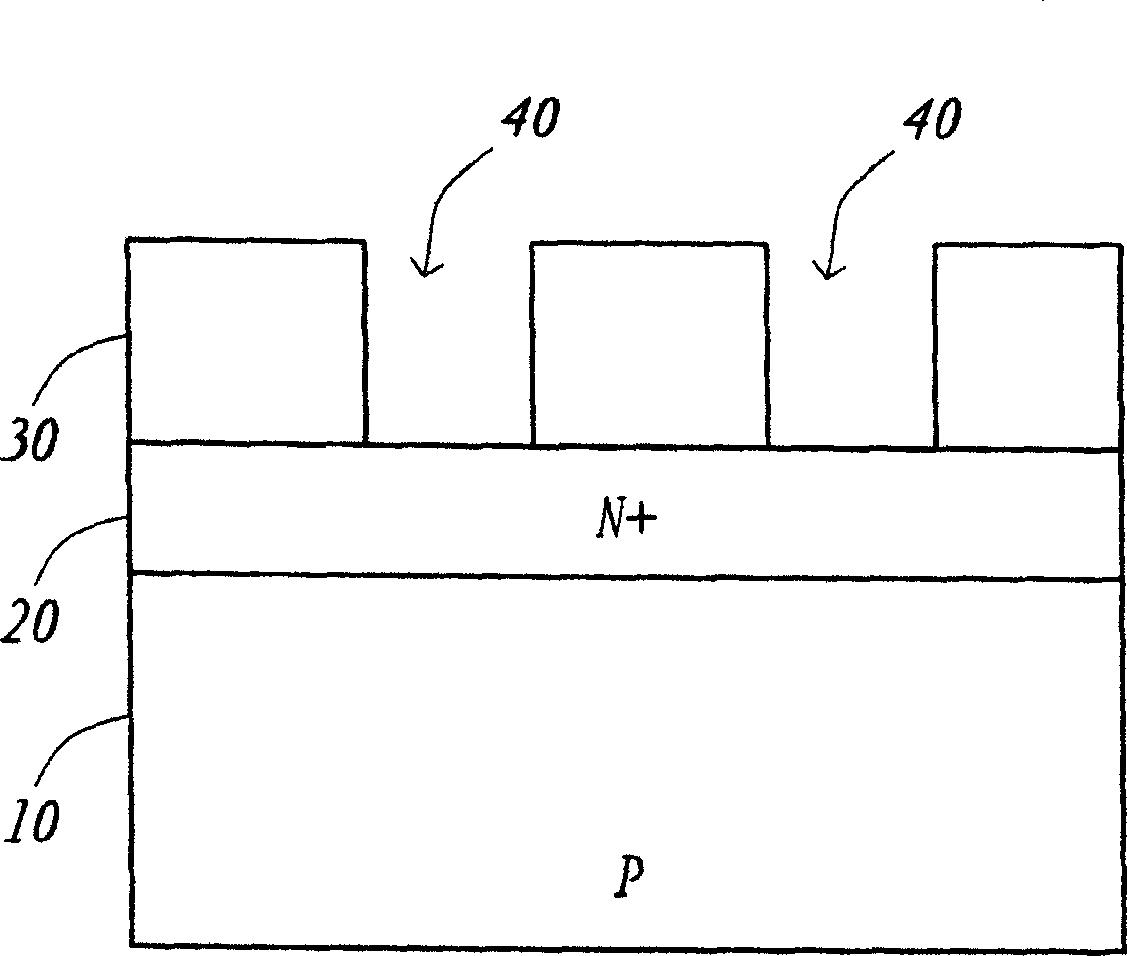

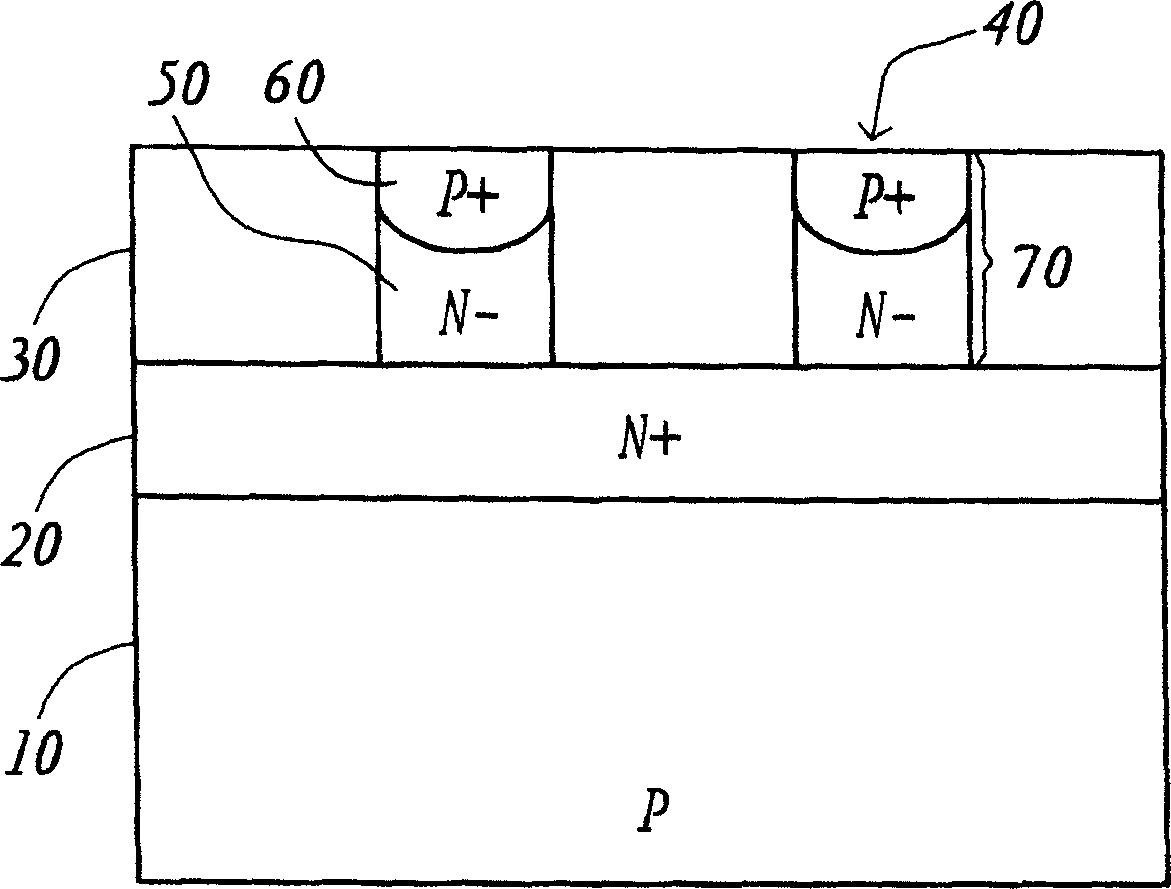

[0019] exist Figure 1B In the dielectric layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com