Memory controller for improving data integrity and operation method thereof

A memory controller and data integrity technology, applied in random number generators, digital data protection, electrical digital data processing, etc., can solve problems such as signal integrity issues, undisclosed modular ECC implementation methods, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

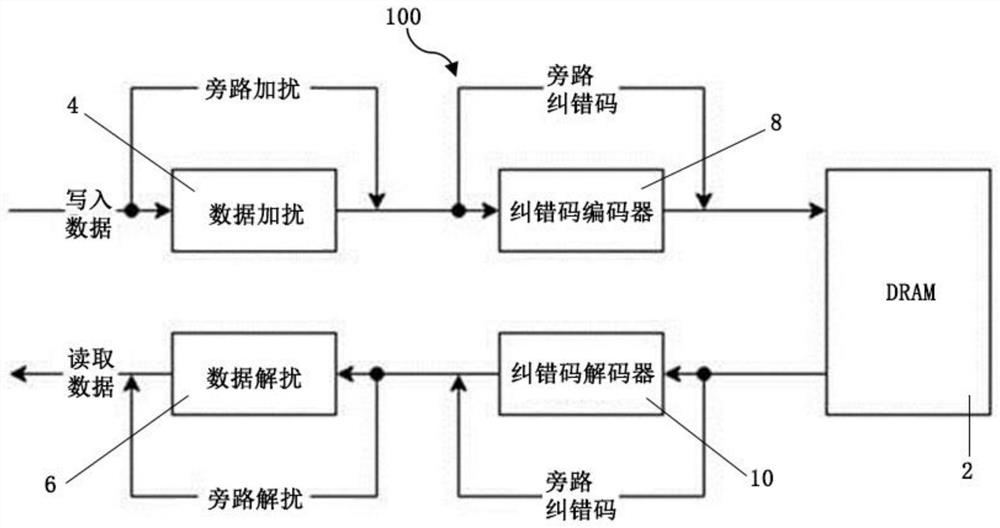

[0041] According to a first embodiment of the method of operating a memory controller (100), the method further comprises the step of: encoding the scrambled data by an error correction code encoding component (8) before transferring the scrambled data to the memory device (2) to encode.

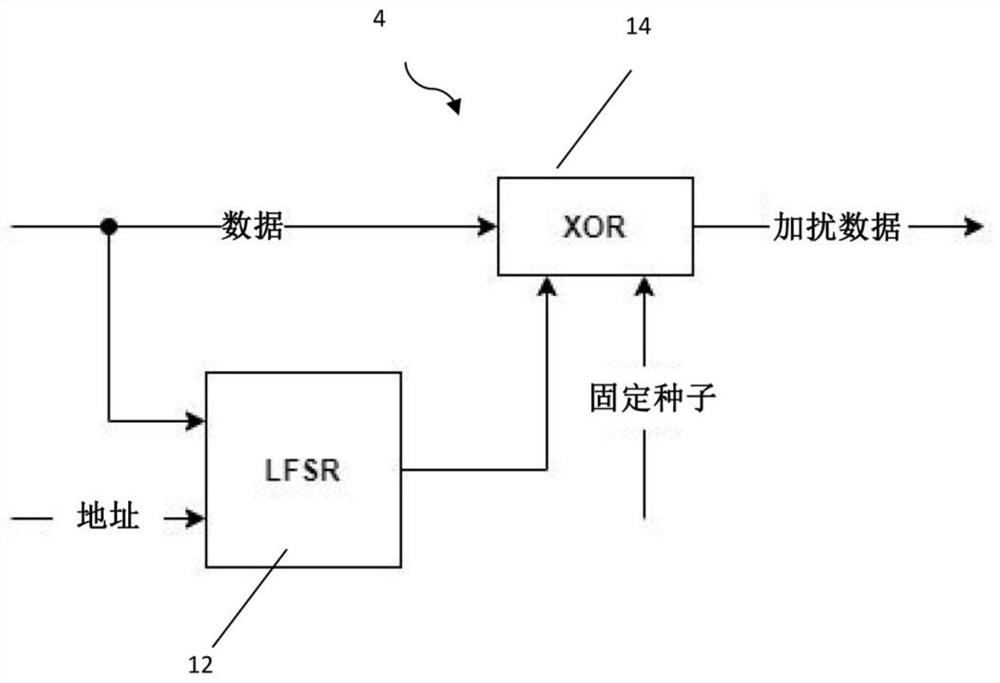

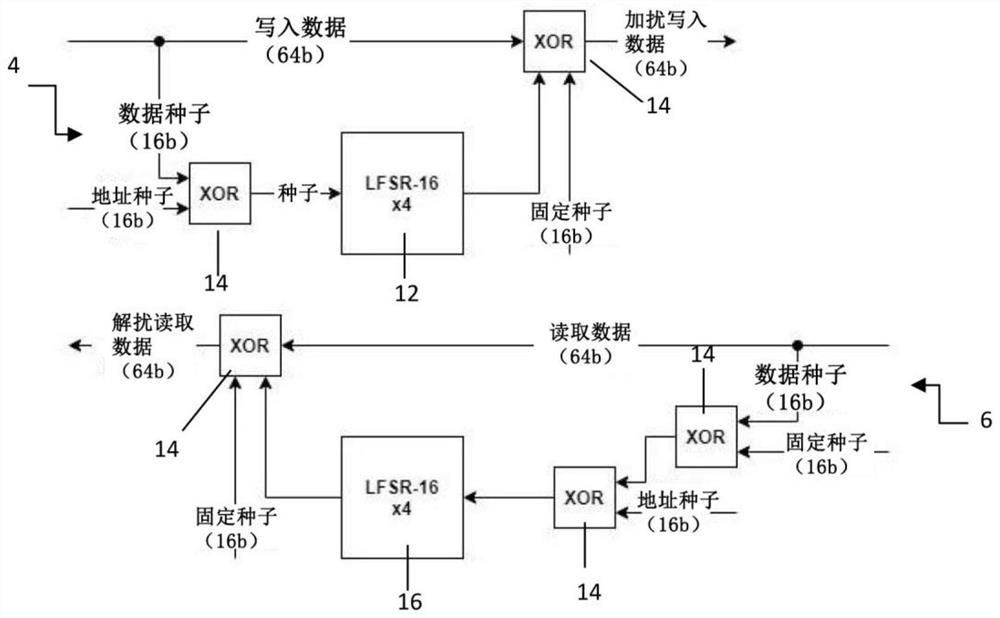

[0042] According to a first embodiment of the method of operating a memory controller (100), the method further comprises the steps of: receiving read data from the memory device (2) in a receive data path; Decoding the data; dividing the read data into a first part and a second part; based on the first part of the read data and a fixed seed corresponding to the first part of the read data, generating an output through a first XOR logic (14) ; According to the output and the address associated with the read data, a pseudo-random output is generated by the descrambling logic (16); by the second XOR logic (14), in response to the pseudo-random output, a second portion of the read data is perfo...

no. 2 example

[0044]According to a second embodiment of the method of operating a memory controller (100), the method further comprises the steps of: receiving read data from the memory device (2) in a receive data path; dividing the read data into a first part and a second part part; based on the first part of the read data and a fixed seed corresponding to the first part of the read data, an output is generated by a first XOR logic (14); based on the output and the address associated with the read data, by descrambling Logic (16) generates a pseudo-random output; by second XOR logic (14), descrambling the second portion of the read data in response to the pseudo-random output, and in response to a fixed corresponding to the first portion of the read data seed, descramble the first part of the read data, thereby generating descrambled data; and decode the descrambled data by an error correction code decoding component (10).

[0045] The memory controller (100) described above overcomes the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com