Security chip, multi-task scheduling method and device thereof and storage medium

A technology of security chip and scheduling method, which is applied in the directions of multi-programming device, climate sustainability, program startup/switching, etc., can solve the problems of thread switching and CPU empty loss, affecting execution speed, and losing multiple switching time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

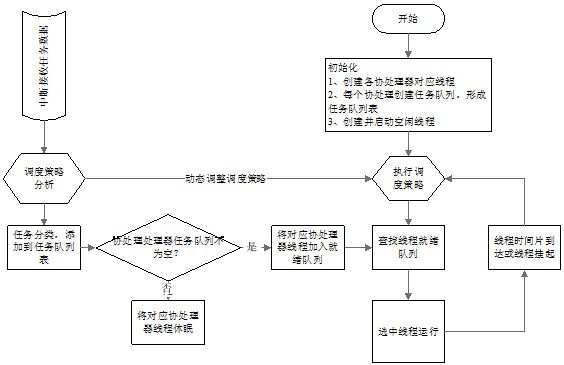

[0041] The following examples of the present invention are described in detail. The example of the embodiment is shown in the attached figure. The same or similar labels from beginning to end indicate the same or similar components or components with the same or similar function. The implementation examples described by reference to the attachment are examples, which are designed to explain the present invention, and cannot be understood as restrictions on the invention.

[0042] The following refers to the multi -tasking scheduling method of the security chip proposed by the embodiment of the present invention, the multi -tasking scheduling device of the security chip, the computer readable storage medium and the security chip.

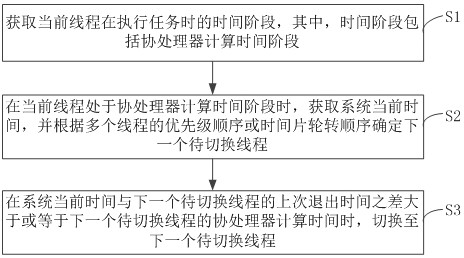

[0043] figure 1 In order to follow the multi -tasking scheduling method of the security chip embodiment of the present invention.

[0044] like figure 1 The multi -tasking scheduling method of the security chip embodiment of the present invention may in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com