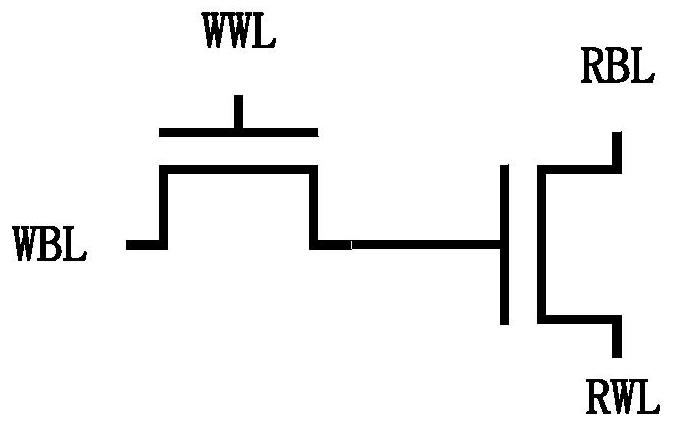

Capacitance-free DRAM (Dynamic Random Access Memory) unit structure and manufacturing method

A technology of cell structure and manufacturing method, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of large occupied area and low integration density, so as to reduce process manufacturing costs, improve integration, and reduce unit area. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

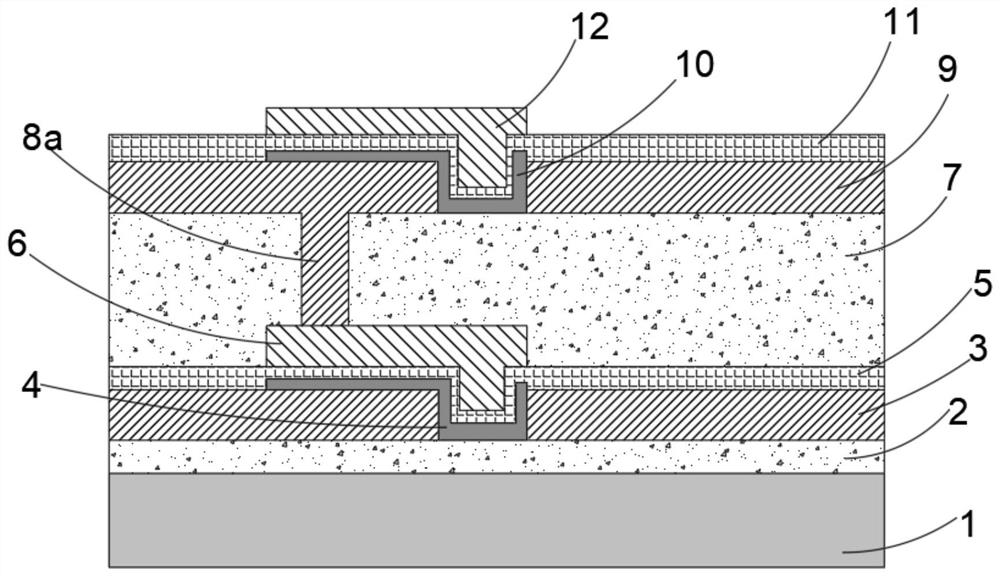

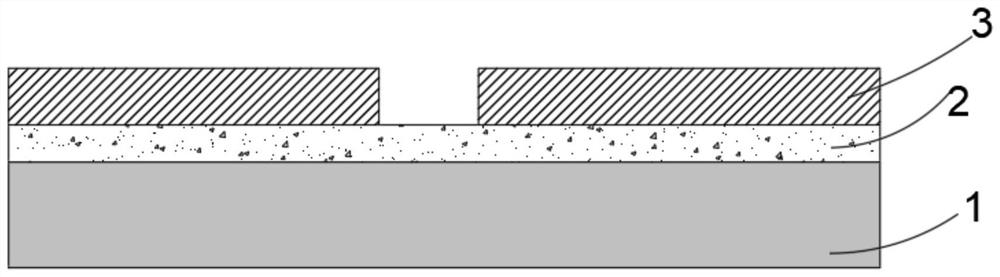

Embodiment Construction

[0031] Hereinafter, embodiments of the present disclosure will be described with reference to the accompanying drawings. It should be understood, however, that these descriptions are exemplary only, and are not intended to limit the scope of the present disclosure. Also, in the following description, descriptions of well-known structures and techniques are omitted to avoid unnecessarily obscuring the concepts of the present disclosure.

[0032] Various structural schematic diagrams according to embodiments of the present disclosure are shown in the accompanying drawings. The figures are not to scale, some details have been exaggerated for clarity, and some details may have been omitted. The shapes of the various regions and layers shown in the figures, as well as their relative sizes and positional relationships are only exemplary, and may vary in practice due to manufacturing tolerances or technical limitations, and those skilled in the art will Regions / layers with differen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com