Nested delay lock ring

A delay-locked ring and nesting technology, which is applied in the direction of automatic power control, electrical components, special data processing applications, etc., can solve the problem of increasing the total delay of the clock or signal path, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

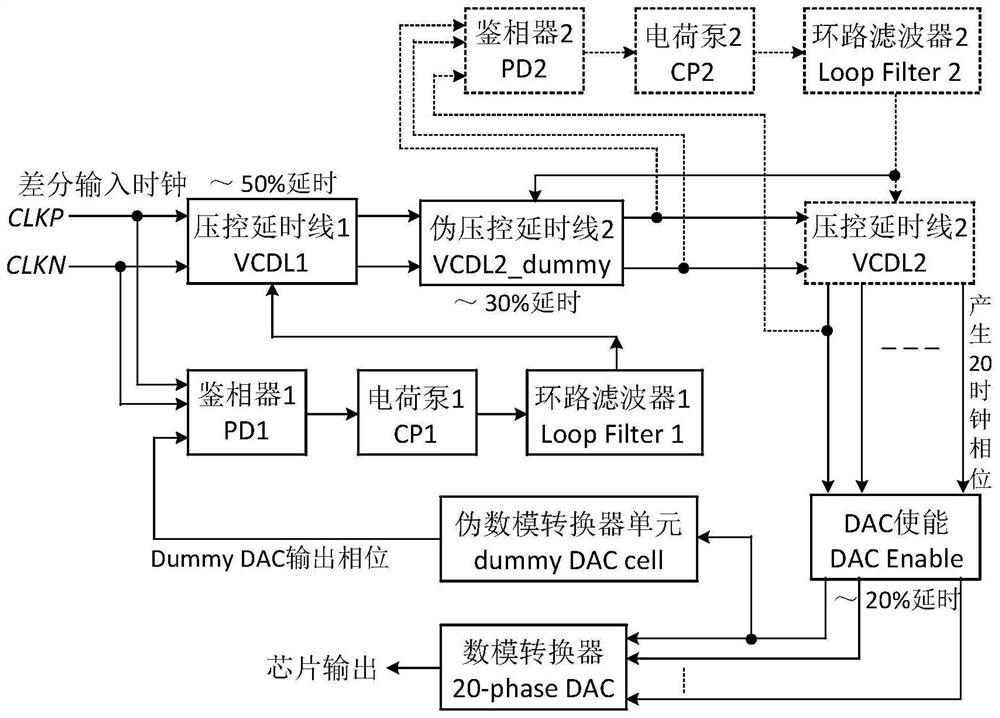

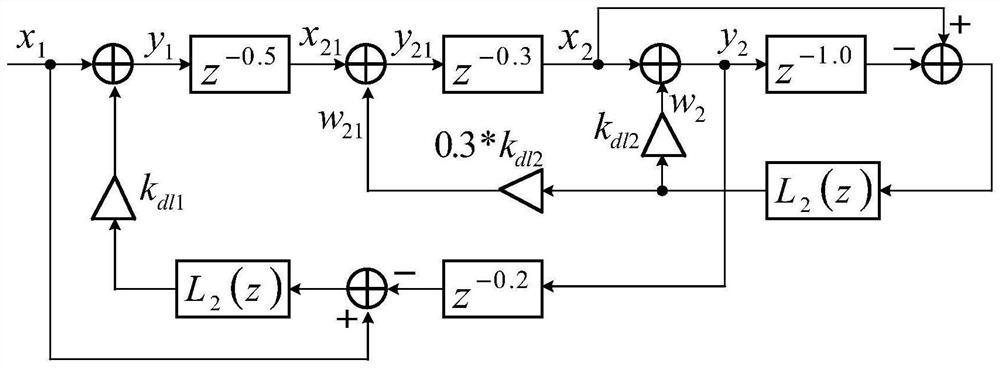

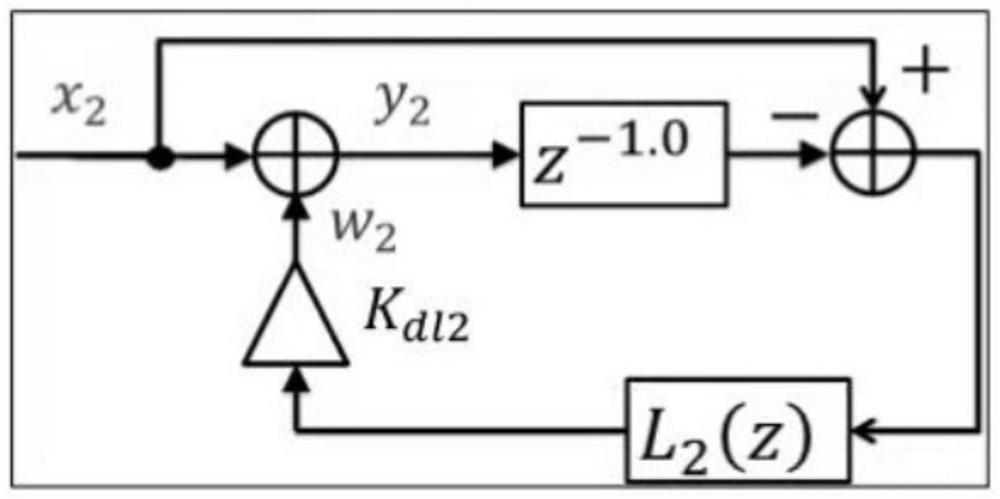

[0026] figure 1 It is a functional block diagram of the nested delay locked loop embodiment of the present invention. The function of the first delay-locked loop (DLL1) is to synchronize the output of the final 20-phase digital-to-analog converter (20-phase DAC) with the input differential clock (CLKP and CLKN), and the total loop delay is Minimum value, i.e. one clock cycle; In view of the fact that the actual DAC output cannot be directly used as phase feedback, the present invention uses the output of a matched dummy DAC cell (dummy DAC cell) to generate the feedbac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com