Testing method of semiconductor structure

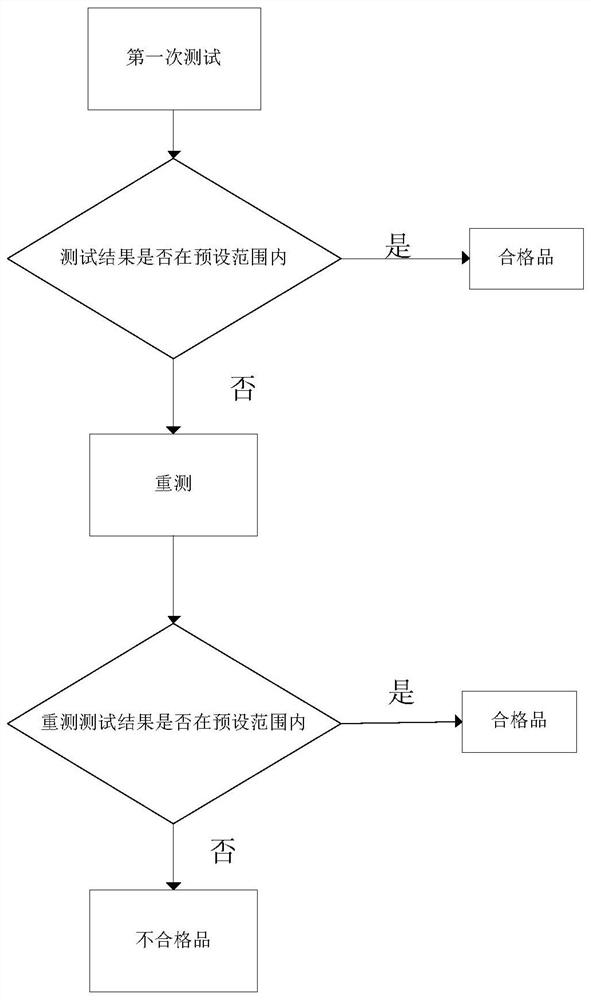

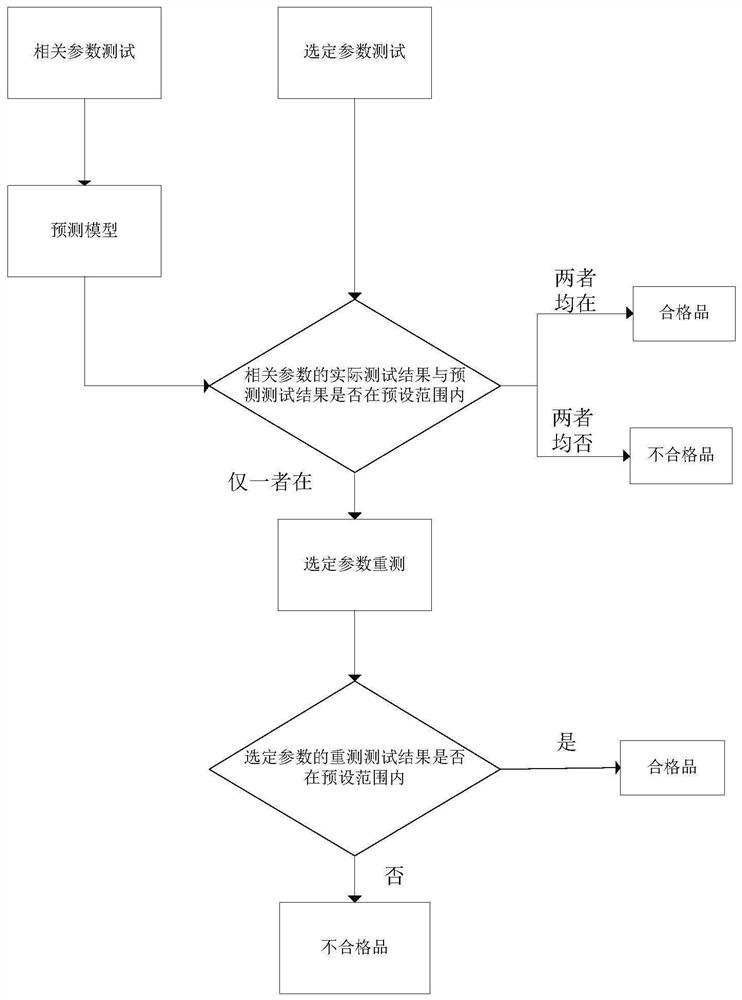

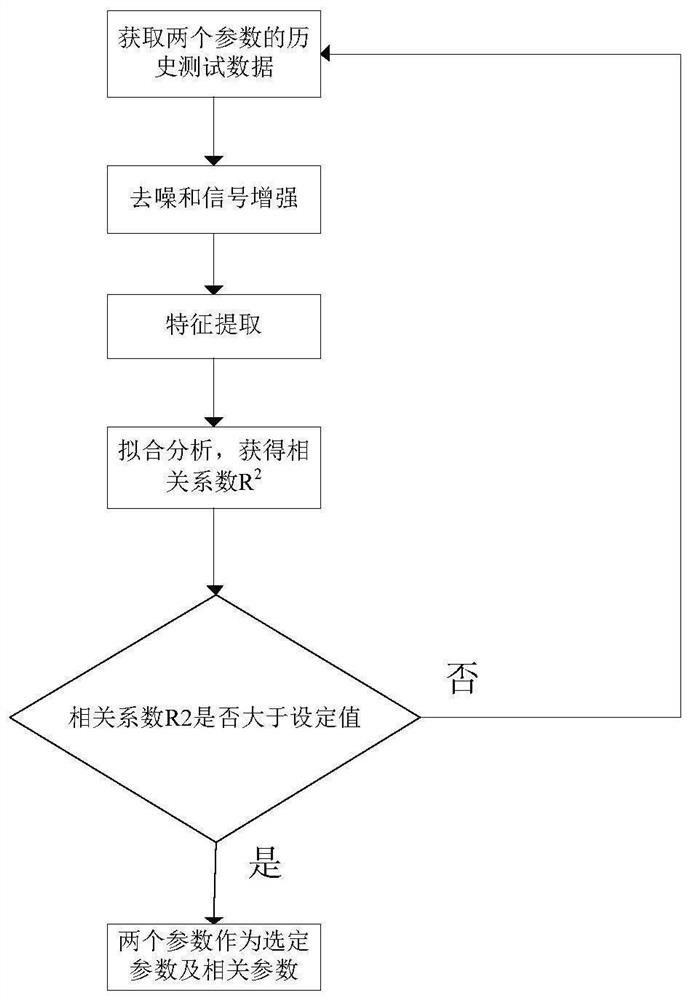

A test method and semiconductor technology, applied in the semiconductor field, can solve problems such as test errors, adverse effects, and misplaced clients, and achieve the effects of reducing display errors, improving test productivity, and reducing retest rates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the purpose, advantages and features of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. It should be noted that the drawings are all in very simplified form and not drawn to scale, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention. In addition, the structures shown in the drawings are often a part of the actual structure. In particular, each drawing needs to display different emphases, and sometimes uses different scales.

[0023] As used in the present invention, the singular forms "a", "an" and "the" include plural objects, the term "or" is usually used in the sense of including "and / or", and the term "several" Usually, the term "at least one" is used in the meaning of "at least one", and the term "at least two" is usually used in the meaning of "two or more". In a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com