Method for solving compatibility and adaptation of different chip pins

A pin configuration and pin technology, applied in the fields of instruments, electrical digital data processing, etc., can solve problems such as unanticipated special needs that are difficult to meet, chip application scenarios, and defects in chip function application scenarios, so as to reduce costs, The effect of improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

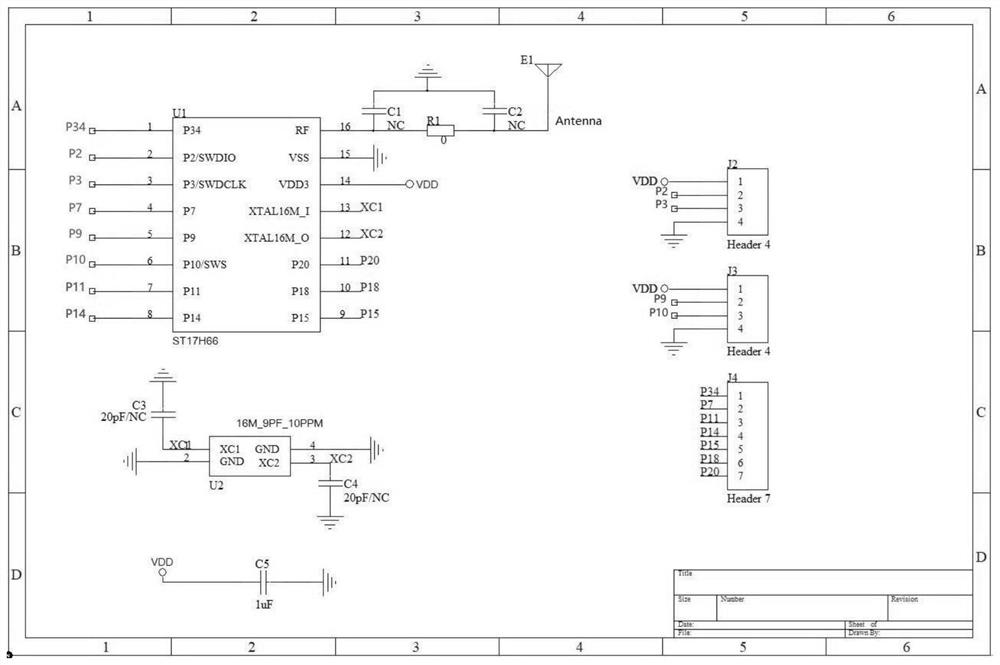

[0041] figure 1 The example chip structure diagram of the present invention is compatible with two kinds of chip pins.

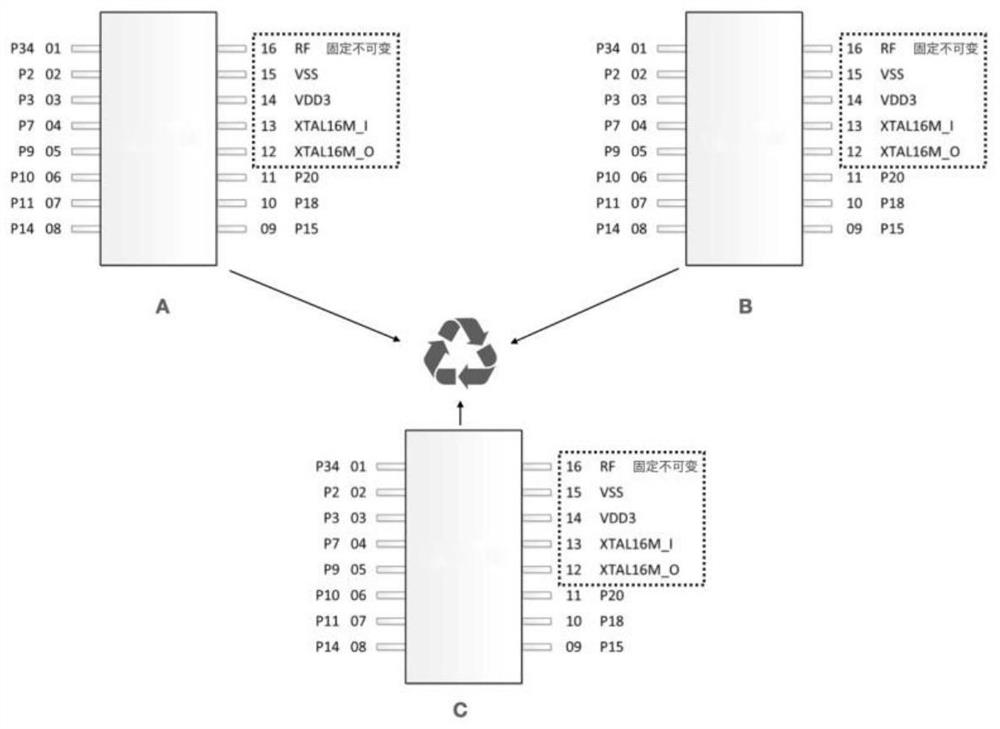

[0042] figure 2 A on the left side above is the pin configuration of the first type of chip, and B on the right side above is the pin configuration of the second type of chip. Using the method of c in the present invention, it can be packaged to be compatible with the first type of chip at the same time Two kinds of chips of chip A and the second type of chip B (lower part in the figure).

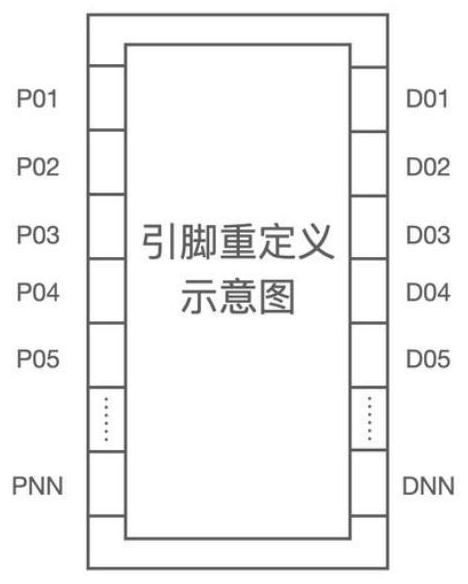

[0043] Such as image 3 P01, P02, and ~PNN shown represent the pin function positions of the chip. Under the control of the editable IO MUX function, the interface positions can be remade to achieve the effect that the chip pins are compatible and adapted.

[0044] Figure 4 Provide the logic structure diagram of IO MUX for the present invention, from P00 to P10, there are 11 configurable contacts in total. Peripheral module IOs mapping via IOMUX mapping. Periph...

Embodiment 2

[0051] In the following, in the programmable IO MUX function mode, the pins with the I2C bus interface mode are compatible and adapted to GPIO as an example to describe in detail.

[0052] The programmable IO MUX function is to provide a flexible I / O configuration, the ports of most peripheral devices can be configured and mapped to any physical I / O contacts (even die boundaries). Among them, peripheral modules include I2C 0-1, I2S, UART, PWM 0-5, SPI 0-1, quadrature decoder, etc. However, for other specific purpose peripherals, their IOs mapping is fixed when enabled, these special purpose peripherals include JTAG, analog_ios, GPIOs and key scan.

[0053] Such as Figure 5 The example chip structure diagram of the present invention is compatible with two kinds of chip pins.

[0054] Such as Figure 6 When described in specific implementation, configuration module is made up of GPIO configuration module, I2C bus configuration module and selector etc., wherein, GPIO configu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com