ESD protection device for fully-depleted silicon-on-insulator and preparation method of ESD protection device

A silicon-on-insulator, ESD protection technology, used in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve the problems of difficulty in preparing high-voltage ESD protection devices, narrowing windows, and many chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

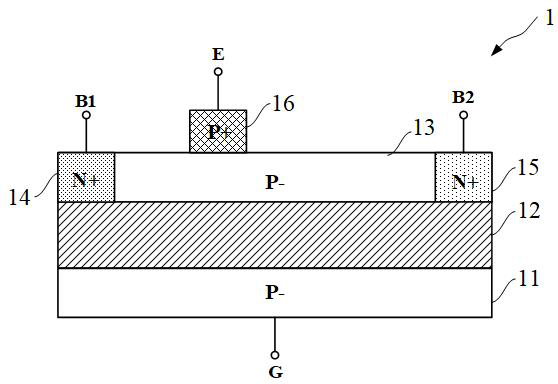

[0044] Such as figure 1 As shown, this embodiment provides a fully depleted silicon-on-insulator ESD protection device 1. The fully depleted silicon-on-insulator ESD protection device 1 includes: a bottom silicon 11, a buried oxide layer 12, a top silicon 13, a first N Type heavily doped region 14, second N type heavily doped region 15, P type heavily doped region 16, first base electrode B1, second base electrode B2, emitter electrode E and gate electrode G.

[0045] Such as figure 1 As shown, the underlying silicon 11 is located at the bottom of the fully depleted silicon-on-insulator ESD protection device 1 .

[0046] Specifically, in this embodiment, the underlying silicon 11 has P-type low doping, the doping ion is boron, and the doping concentration is 10 15 cm -3 ; In actual use, the corresponding doping ions and doping concentration can be selected according to actual needs, not limited to this embodiment.

[0047] Such as figure 1 As shown, the buried oxide layer...

Embodiment 2

[0069] Such as Figure 6~Figure 8 As shown, this embodiment provides a method for manufacturing a fully depleted silicon-on-insulator ESD protection device. As an example, the structure of the fully depleted silicon-on-insulator ESD protection device is the same as that of the first embodiment. The preparation method of the fully depleted silicon-on-insulator ESD protection device comprises:

[0070] S1: Provide a P-type SOI structure, the SOI structure includes a bottom layer of silicon, a buried oxide layer and a top layer of silicon stacked in sequence.

[0071] Specifically, such as Figure 6 As shown, this embodiment is based on the fully depleted silicon-on-insulator process, and firstly an SOI substrate structure is provided, and the SOI substrate structure includes the bottom silicon 11 , the buried oxide layer 12 and the top silicon 13 stacked in sequence. The method for preparing the SOI substrate structure is not limited, and any method that can obtain the SOI sub...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com