A chip stack and its preparation method

A chip stacking and carrier technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of polluting the active area of semiconductor components and poor bonding stability of semiconductor components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to better understand the technical solutions of the present invention, the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

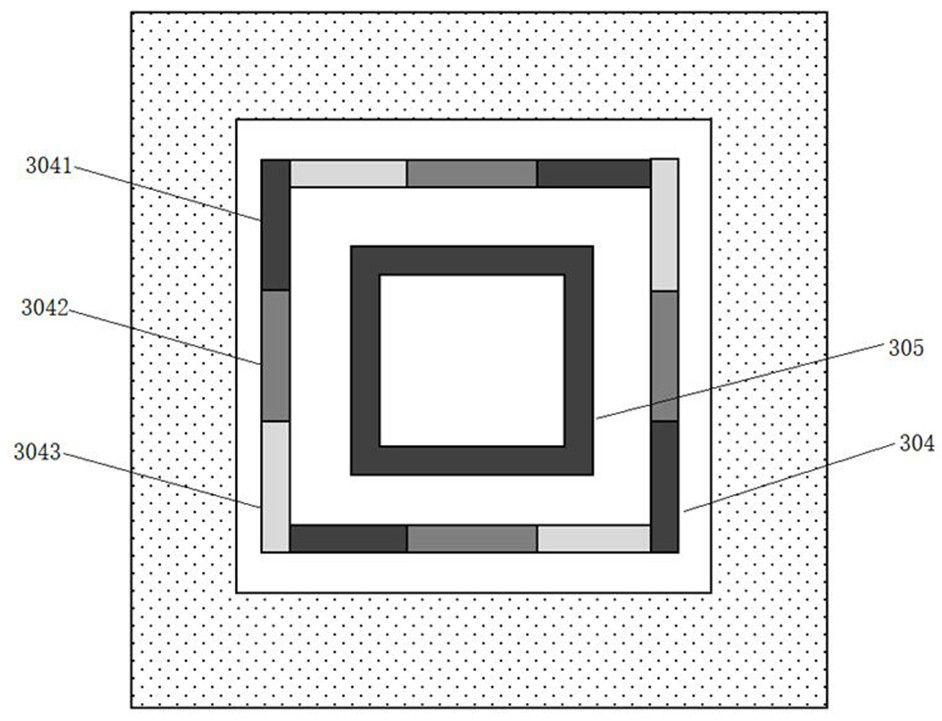

[0037] The present invention proposes a method for preparing a chip stack, comprising the following steps:

[0038] Step (1): A first carrier is provided, a first adhesive layer is arranged on the first carrier, a plurality of first semiconductor elements are arranged on the first adhesive layer, and the functional areas of the first semiconductor elements contacting the first adhesive layer.

[0039] Step (2): disposing a first sacrificial material layer on the first bonding layer, the first sacrificial material layer wrapping the side of the first semiconductor ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com