Three-dimensional memory

A memory, three-dimensional technology, applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., to achieve the effect of improving bonding reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

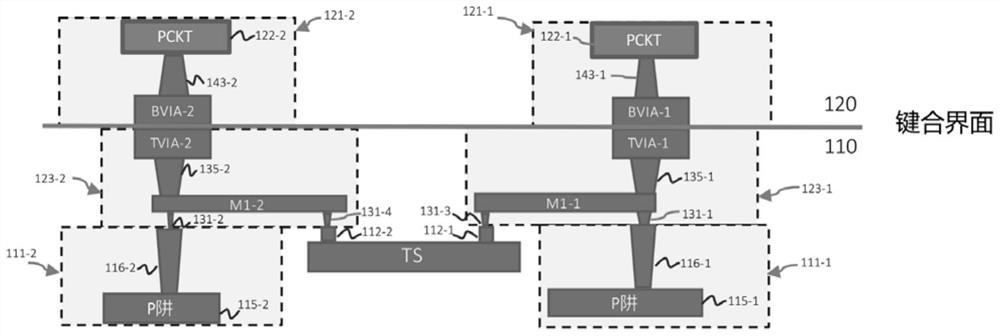

[0030] For a better understanding of the application, various aspects of the application will be described in more detail with reference to the accompanying drawings. It should be understood that these detailed descriptions are descriptions of exemplary embodiments of the application only, and are not intended to limit the scope of the application in any way. Throughout the specification, the same reference numerals refer to the same elements. The expression "and / or" includes any and all combinations of one or more of the associated listed items.

[0031] It should be noted that in this specification, expressions such as first, second, third, etc. are only used to distinguish one feature from another, and do not represent any limitation on the features, especially do not represent any sequential order. Thus, a first side discussed herein could also be termed a second side, and a first window could also be termed a second window, and vice versa, without departing from the teac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com