Partial bit stream read-back technology for testing internal resources of an FPGA

A technology of internal resources and technology, applied in the field of FPGA testing, can solve the problems of complete FPGA testing, poor versatility, limited storage space, etc., to save readback time, improve test efficiency, and achieve simple results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the purpose, technical solutions and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific drawings and embodiments:

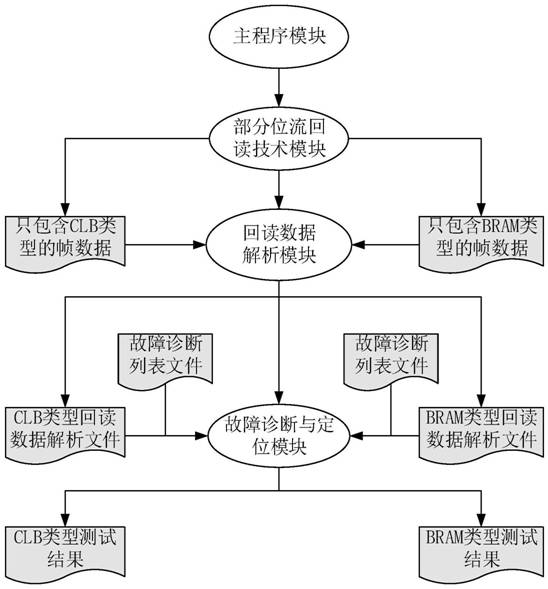

[0025] The partial bit stream readback technology proposed by the present invention, its overall realization framework is as follows figure 1 As shown, it specifically includes the following:

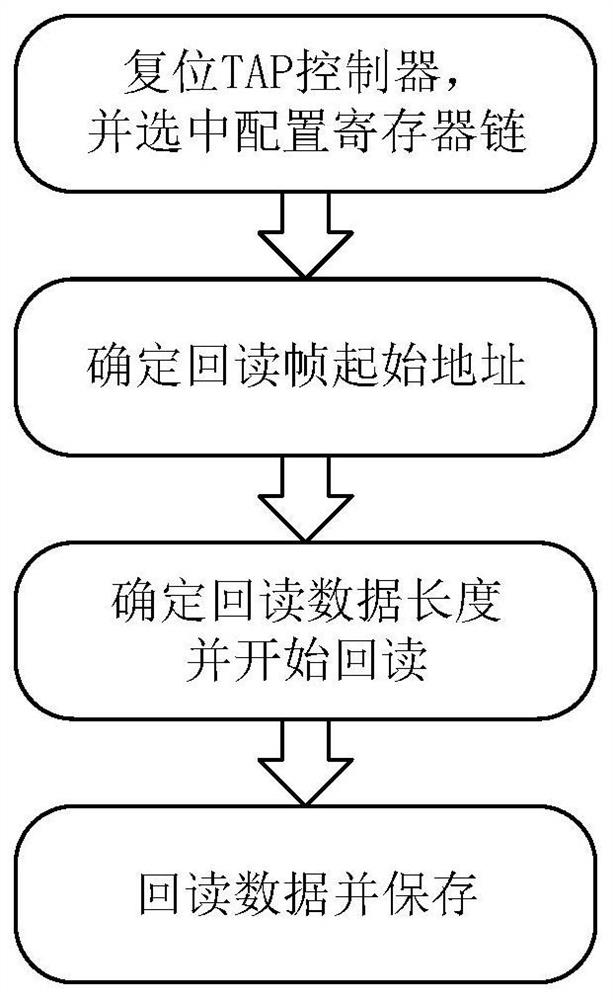

[0026] Step 1. After configuring the FPGA, reset the TAP controller first, and then select the FPGA configuration register chain. Such as figure 2 Shown is the boundary-scan architecture of JTAG. All information (instructions, test data and test results) exchanged with the outside of the chip based on boundary-scan technology adopts serial communication, and the test instructions and related test Data is written into the chip, and then the execution result of the test command is read out from the chip in a serial manner.

[0027] Step 2: Write the start addres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com