A kind of wafer chip cutting method

A cutting method and cutting direction technology, applied in the manufacturing of electrical components, circuits, semiconductor/solid-state devices, etc., can solve the problems of tool damage, chip nicks or cracks, tool collision, etc., to reduce the number of changes and simplify the tool cutting process. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

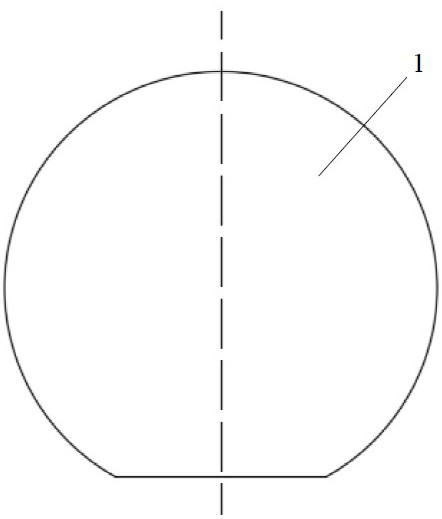

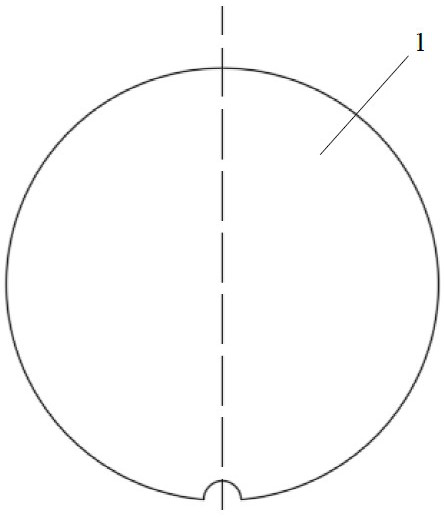

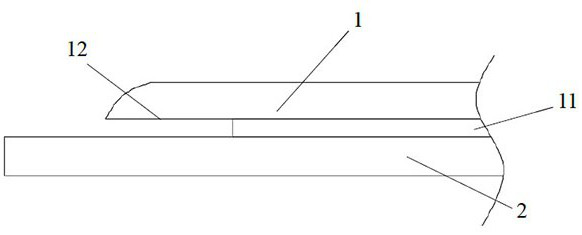

[0033] Such as Figure 6-7 As shown, it is a wafer chip cutting method in this embodiment. After cutting all the first cutting lines 6 in the first cutting direction, the tool cuts all the second cutting lines 7 in the second cutting direction. The cutting direction and the second cutting direction are perpendicular to each other, and the first cutting direction is parallel or perpendicular to the central axis of the wafer chip 1, and at least in the second cutting direction, the cutting position of the cutter is at In the effective area of the wafer chip 1 . Further, the first cutting direction is parallel to the central axis of the wafer chip 1 and is longitudinal, and the second cutting direction is perpendicular to the central axis of the wafer chip 1 and is transverse. In other embodiments, the first cutting direction may be transverse and the second cutting direction may be longitudinal. All of the first cutting lines 6 are parallel to the central axis and adjacent t...

Embodiment 2

[0041] Such as Figure 8 As shown, this embodiment is a wafer chip cutting method, which is different from the cutting method in Embodiment 1 in that the entry position or exit position of all the first dicing lanes 6 is in the second cutting direction Not flush, all close to the edge of the wafer chip 1 . The feeding positions of all the second dicing lines 7 are not flush in the first cutting direction, and are all close to the edge of the wafer chip 1 . Such a design is beneficial to reduce the cutting length of the cutter and consume less time.

Embodiment 3

[0043] This embodiment is a wafer chip cutting method, which is different from the cutting method in Embodiment 1 in that, in the second cutting direction, the cutter is in the same second cutting line 7, first from left to The first cutting is performed on the right, and then the second cutting is performed from right to left. The knife exit positions of the two cuttings are all located at the same position in the effective area. Then the cutter cuts all the second cutting lines 7 one by one. Using the cutting method of this embodiment, although the cutter needs to change direction when cutting the same second cutting line 7, compared with Embodiment 1, the stage carrying the wafer chip 1 does not need to be provided with a driving device to Rotating the wafer chip 1 reduces equipment requirements.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com