Memory coupling compiling method and system for reconfigurable chip

A compiling method and compiling system technology, applied in the field of reconfigurable processor development, can solve problems such as incorrect use and ambiguous use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

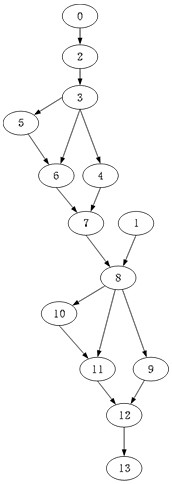

[0039] In order to have a clearer understanding of the technical features, purposes and effects of the invention, the specific embodiments of the present invention are now described with reference to the accompanying drawings, in which the same reference numerals represent components with the same or similar structures but the same functions.

[0040] In this article, "schematic" means "serving as an example, example or illustration", and any illustration or implementation described as "schematic" should not be interpreted as a more preferred or more advantageous Technical solutions. In order to keep the drawings concise, the drawings only schematically show the parts related to this exemplary embodiment, and they do not represent the actual structure and true proportion of the product.

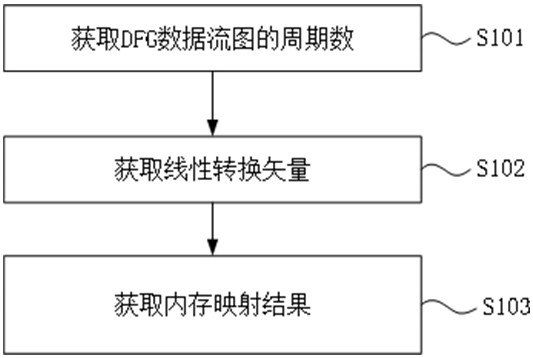

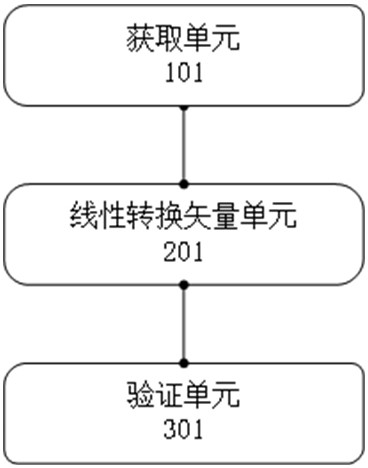

[0041] One aspect of the present invention provides a memory coupling compiling method for a reconfigurable chip, such as figure 1 As shown, the memory-coupled compilation method for reconfi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com