Wafer plastic packaging method, wafer level packaging structure and packaging method thereof, and plastic packaging mold

A technology for plastic packaging molds and wafer-level chips, which is applied in the manufacture of electrical components, circuits, semiconductors/solid-state devices, etc., can solve the problem that the utilization rate of chips needs to be further improved, and achieve the improvement of the problem of plastic packaging eccentricity, increase the utilization rate, and cutting The effect of area reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

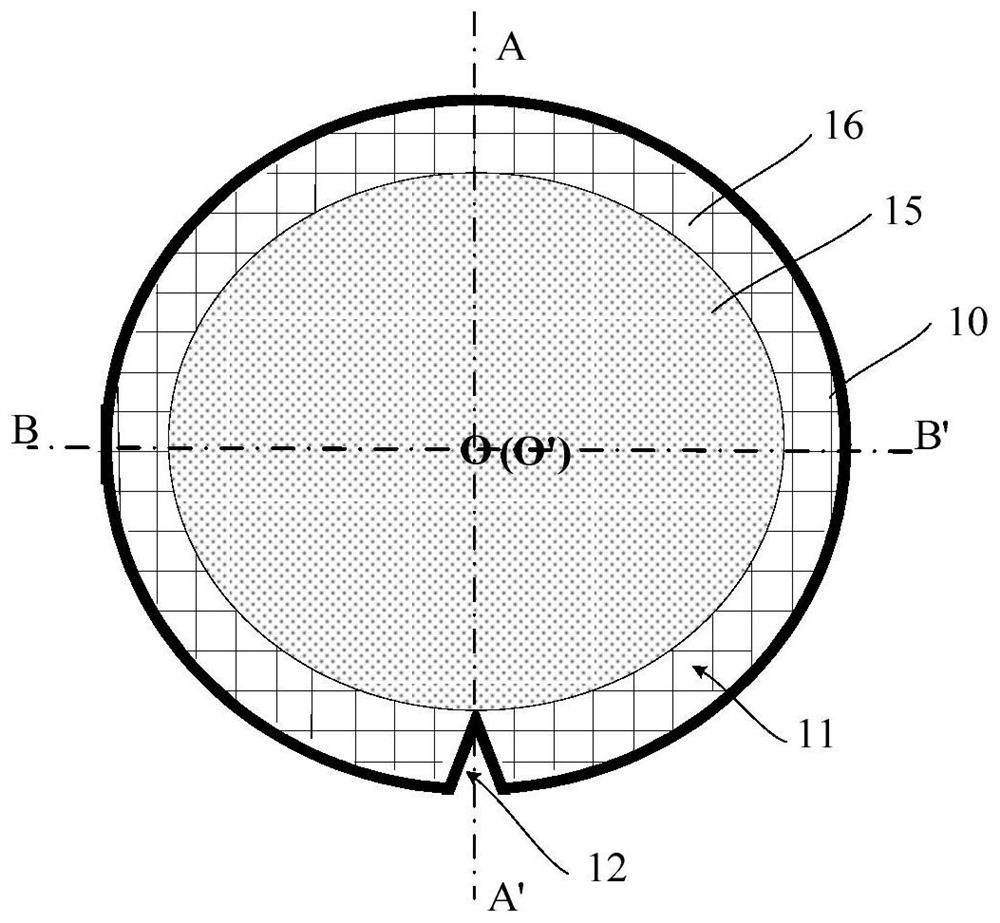

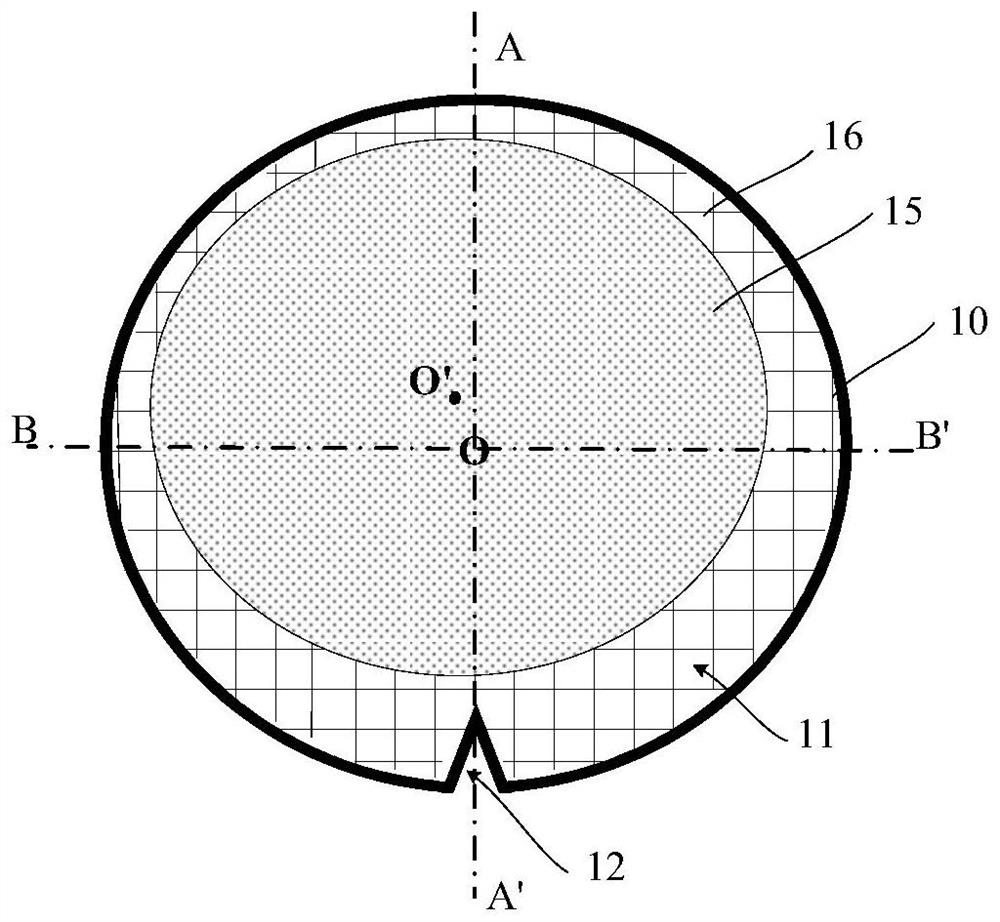

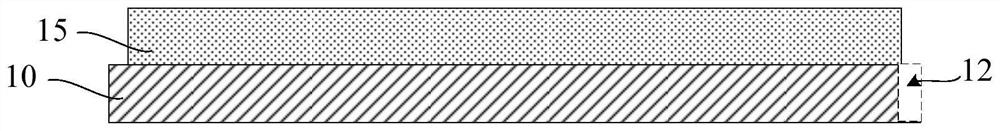

[0057] As we all know, the edge region of the wafer usually has a notch (Notch), which is generally V-shaped, which can be used as a mark for the crystallographic direction of the wafer and plays a role in positioning during the wafer manufacturing process. The inventors found that, in the molding process of wafer level packaging (Wafer Level Package, WLP), when the molding compound (MoldingCompound) on the wafer is heated and pressed until it is close to the size of the wafer, the molding compound will be released from the edge of the wafer. The V-notch overflows. Due to the limitation of the gap on the wafer, in actual molding, the area covered by the molding material on the wafer (that is, the molding area) is often smaller than the area of the wafer to avoid overflow of the molding material.

[0058] Figure 1a It is a schematic diagram of the structure of wafer plastic packaging without eccentricity in the existing process, Figure 1b It is a schematic diagram of the s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com