Wafer polishing device and method

A technology for polishing devices and wafers, which is applied in the direction of grinding devices, electrical components, circuits, etc., which can solve the problems of shortened service life of polishing carriers, decreased flatness of wafers, and increased costs, so as to improve flatness and prolong use The effect of life, polishing process is simple and easy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

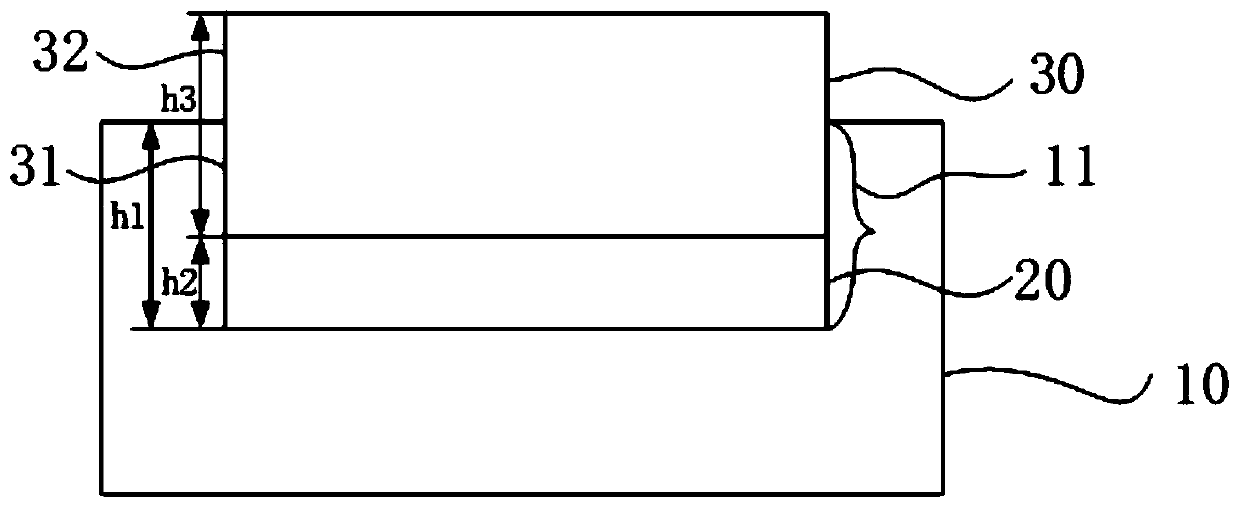

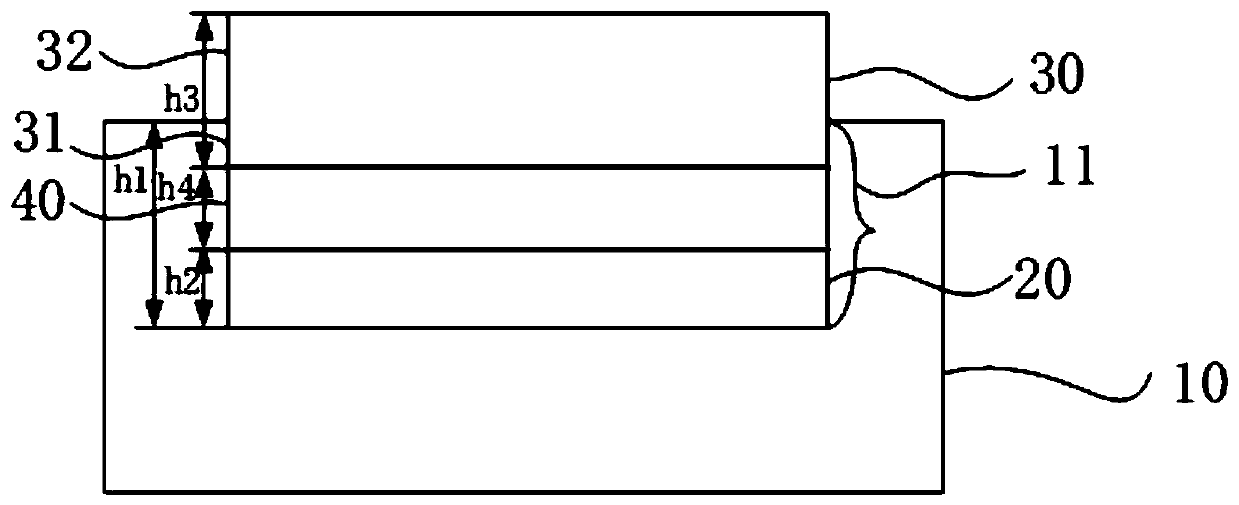

[0031] figure 1 A schematic structural diagram of a wafer polishing device provided in Embodiment 1 of the present invention, as shown in figure 1 As shown, the wafer polishing device includes a polishing carrier 10 and an adjustable thickness polishing pad 20. The polishing carrier 10 includes a polishing carrier groove 11. During the polishing process of the wafer 30, the thickness adjustable polishing pad 20 is arranged on In the polishing carrier slot 11 , the wafer 30 is placed on the polishing pad 20 with adjustable thickness.

[0032] The groove depth h1 of the polishing carrier groove 11 , the thickness h2 of the thickness-adjustable polishing pad, and the thickness h3 of the wafer satisfy h2+h3>h1.

[0033] It should be noted that the thickness-adjustable polishing pad 20 is selected according to the thickness h3 of the wafer 30 . When the sum of the thickness h2 of the thickness-adjustable polishing pad and the thickness h3 of the wafer is greater than the groove d...

Embodiment 2

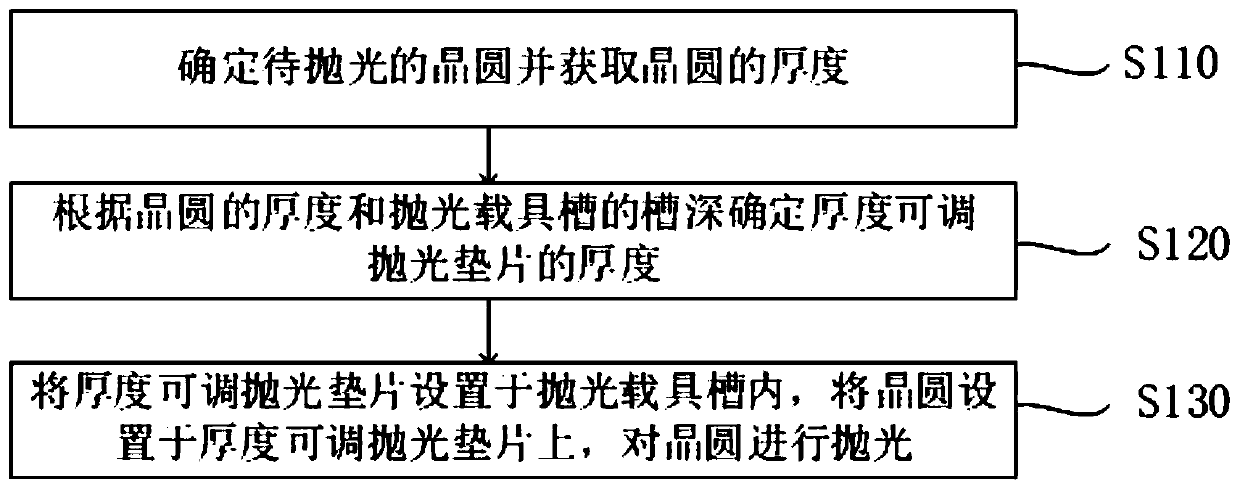

[0055] image 3 It is a schematic flow chart of a wafer polishing method provided in Embodiment 2 of the present invention. A wafer 30 is polished using a wafer polishing device. Refer to Figure 1-3 , the wafer polishing device includes a polishing carrier 10 and a thickness-adjustable polishing pad 20, the polishing carrier 10 includes a polishing carrier groove 11, and the wafer polishing method includes:

[0056] S110. Determine the wafer to be polished and acquire the thickness of the wafer.

[0057] S120. Determine the thickness of the polishing pad with adjustable thickness according to the thickness of the wafer and the groove depth of the polishing carrier groove.

[0058] Wherein, the groove depth h1 of the polishing carrier groove 11 , the thickness h2 of the adjustable thickness polishing pad 20 and the thickness h3 of the wafer 30 satisfy h2+h3>h1.

[0059] S130 disposing the thickness-adjustable polishing pad in the groove of the polishing carrier, setting the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com