Visual memory chip repair analysis program inspection method and device

A technology of memory chips and programs, applied in CAD circuit design, etc., can solve the problems of cumbersome process and time-consuming, and achieve the effect of saving time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

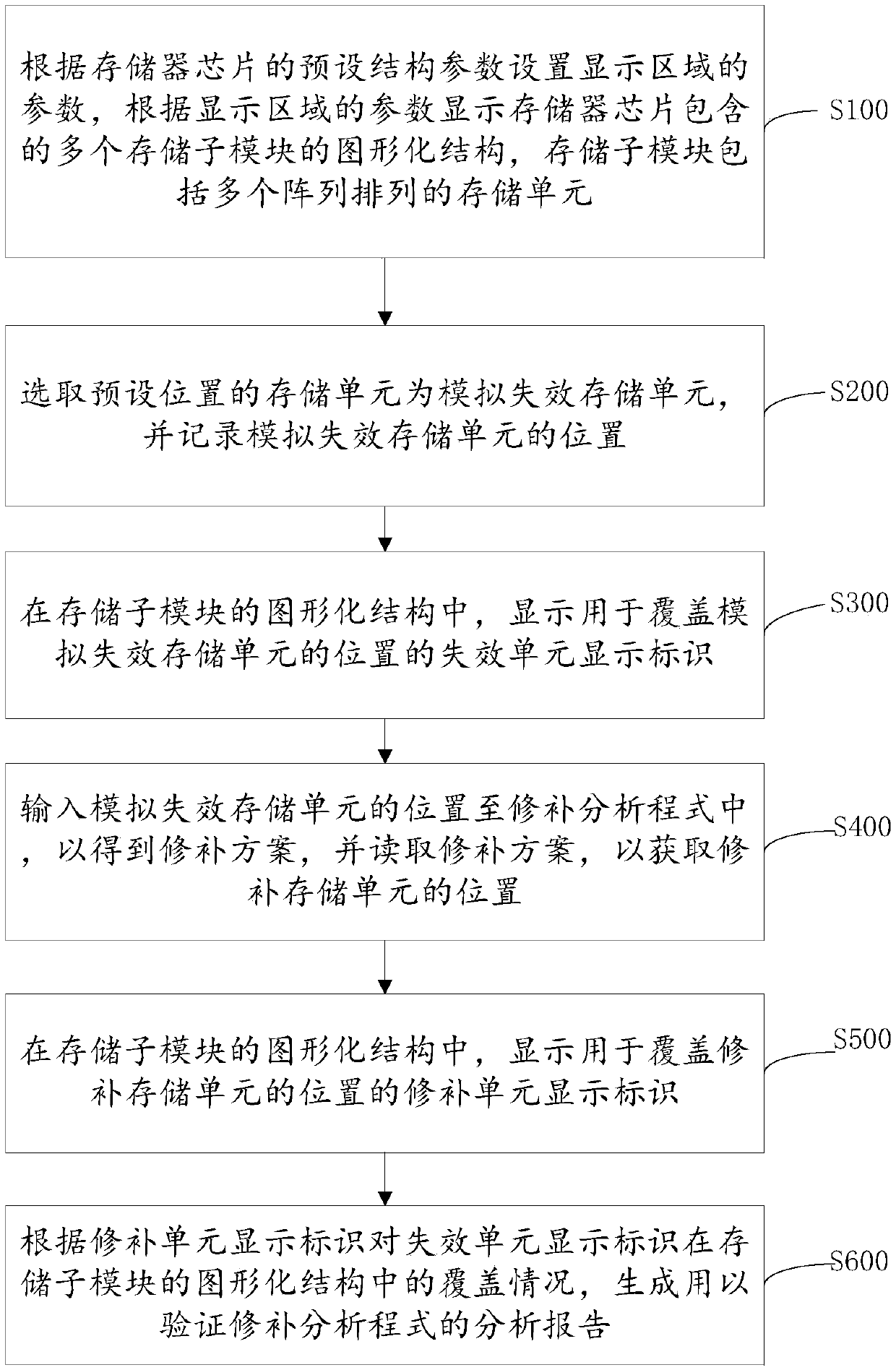

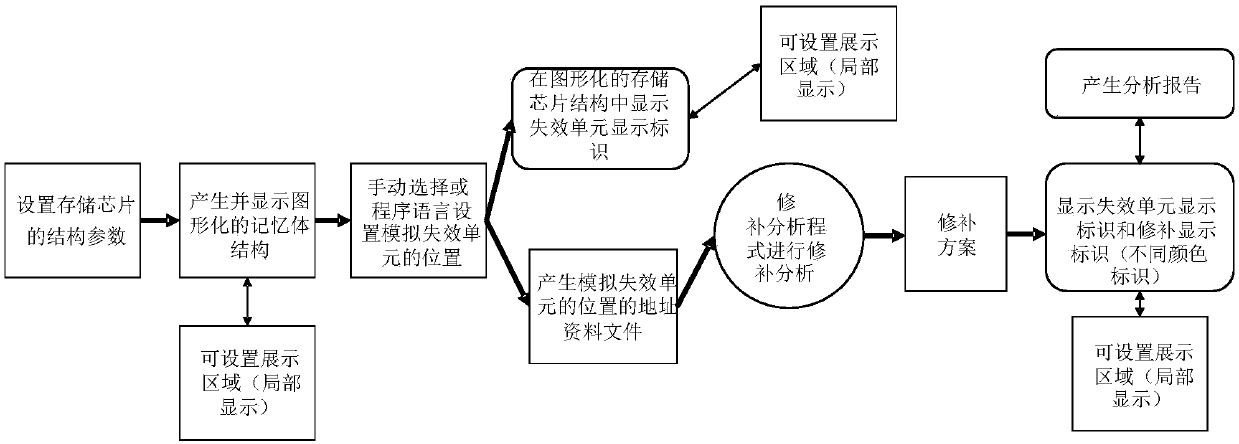

[0075] In a specific embodiment, a visual memory chip repair analysis program verification method is provided, such as figure 1 and image 3 shown, including the following steps:

[0076] Step S100: Set the parameters of the display area according to the preset structural parameters of the memory chip 10, and display the graphical structure 200 of the multiple storage sub-modules contained in the memory chip 10 according to the parameters of the display area. storage unit 210 .

[0077] Such as figure 2 As shown, the memory chip 10 includes a plurality of storage sub-modules 11, and the number of the storage sub-modules 11 can generally be determined according to the total capacity of the memory chip. Each storage sub-module 11 includes a plurality of data bits 12 with a storage array. The memory array is composed of memory cells 210 .

[0078] Such as figure 2 As shown, the preset structural parameters of the memory chip 10 include the total number of memory sub-modul...

Embodiment 2

[0112] The present invention also provides a visual memory chip repair analysis program checking device, such as Figure 8 shown, including:

[0113] The graphical structure setting module 10 is used to set the parameters of the display area according to the preset structural parameters of the memory chip, and display the graphical structure 200 of a plurality of storage sub-modules 11 contained in the memory chip according to the parameters of the display area. The storage sub-module 11 includes A plurality of storage units 210 arranged in an array;

[0114] The simulated failure storage unit setting module 20 is used to select the storage unit 210 of the preset position as the simulated failure storage unit 220, and record the position of the simulated failure storage unit 220;

[0115] The failure unit display mark 230 display module 30 is used to display the failure unit display mark 230 for covering the position of the simulated failure storage unit 220 in the graphical...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com