Method for growing patterned GaN on sapphire template and GaN epitaxial wafer

A patterning and sapphire technology, applied in the direction of gaseous chemical plating, coating, metal material coating process, etc., can solve the problem that etching damage cannot be completely avoided

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

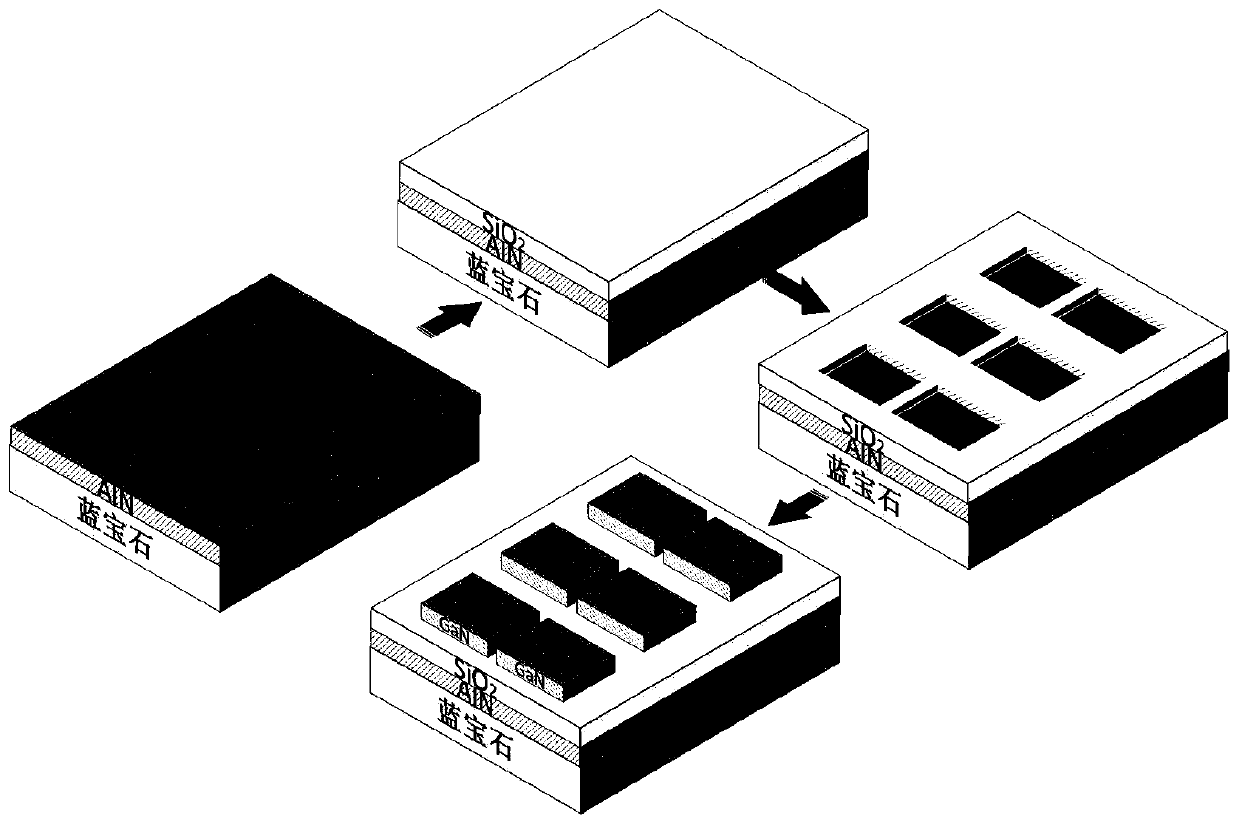

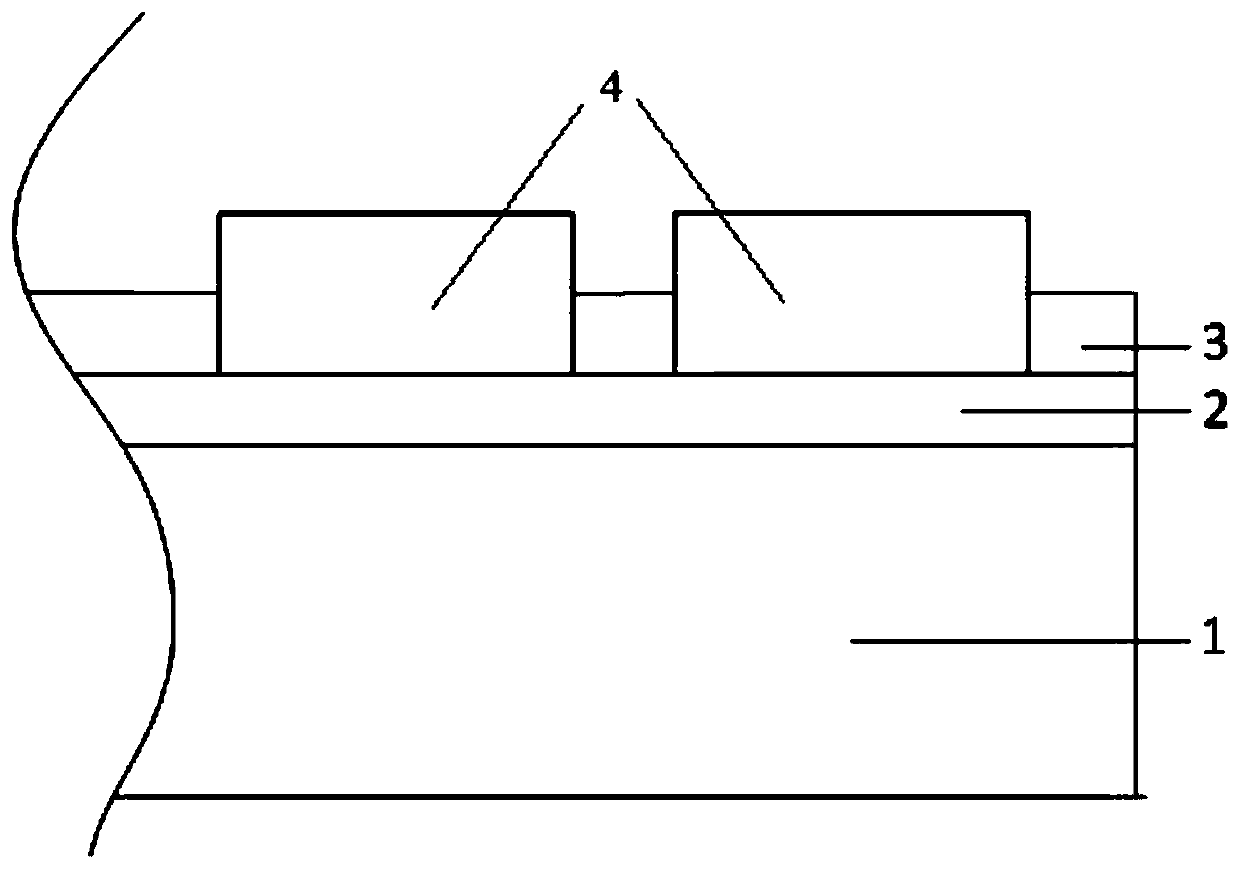

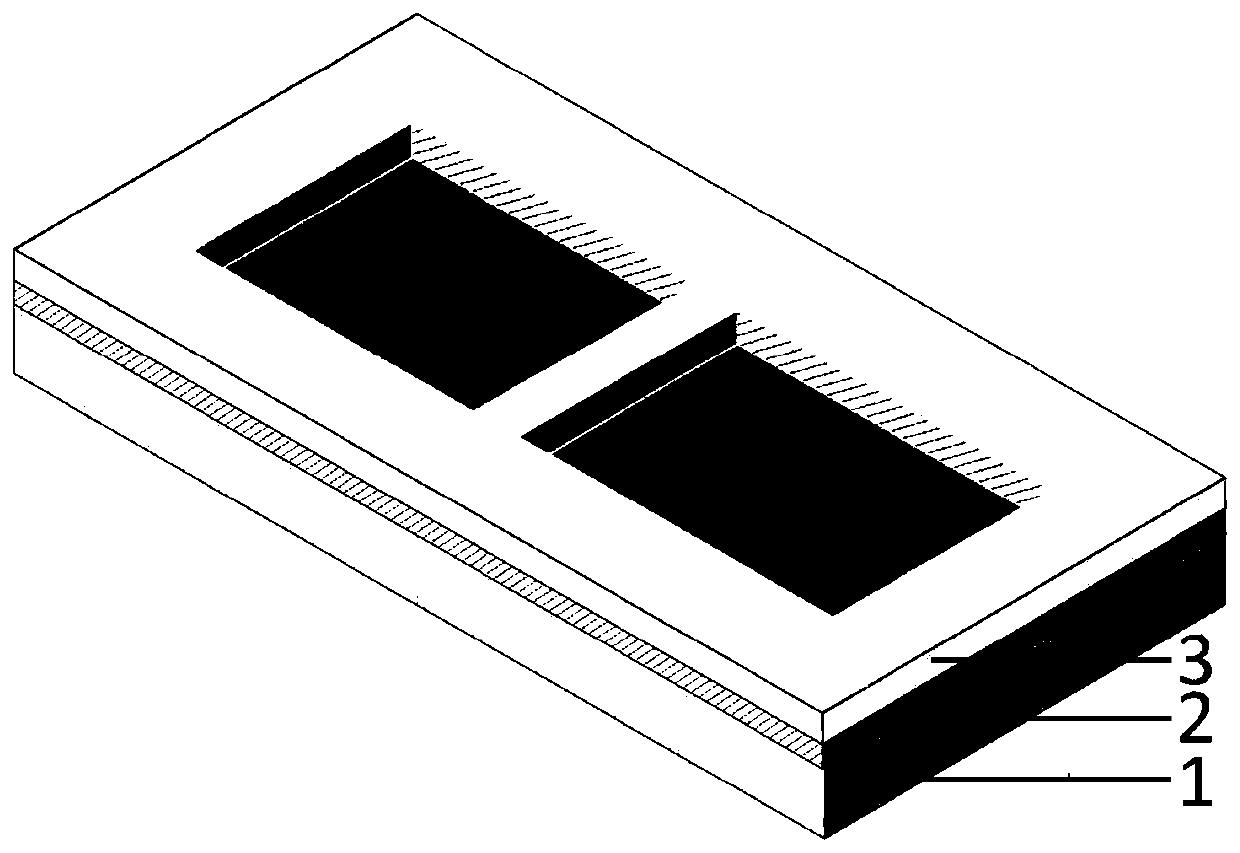

[0041] In this example, the GaN epitaxial wafer required in a terahertz Schottky diode (where the GaN mesa is composed of two 60μm×60μm square raised GaN modules) is taken as an example, and a patterned GaN layer is grown on a sapphire template. The target device The profile of figure 2 As shown, the patterned GaN is specifically two square bump modules, figure 2 Middle: 1 is sapphire substrate, 2 is AlN nucleation layer, 3 is SiO 2 Dielectric layer 4 is a patterned GaN layer.

[0042] Specific steps are as follows:

[0043] (1) Growth of AlN nucleation layer 2 on sapphire substrate 1: place the cleaned sapphire substrate in an MOCVD reaction chamber, and grow a 100nm AlN nucleation layer at 800°C, the Al source and N The source consists of TMAl and NH respectively 3 supply;

[0044] (2) Growth of SiO on the AlN nucleation layer 2 2 Medium layer 3. The cleaned sample (sapphire substrate with AlN nucleation layer grown) was placed in the PECVD reaction chamber and depo...

Embodiment 2

[0050] Other conditions are consistent with embodiment 1, only with SiO 2 The thickness of the dielectric layer is changed to 200nm, and the temperature of the secondary epitaxial growth of GaN is changed to 1100°C.

[0051] Observing the GaN epitaxial wafer obtained after the growth is completed, it can be seen that the side wall of the GaN mesa is smooth, the edge is flat, there is no etching damage, and the mask part (SiO 2 dielectric layer) essentially no GaN deposition.

Embodiment 3

[0053] Other conditions are consistent with embodiment 1, only with SiO 2 The thickness of the dielectric layer is changed to 150nm, and the temperature of the secondary epitaxial growth of GaN is changed to 1050°C.

[0054] Observing the GaN epitaxial wafer obtained after the growth is completed, it can be seen that the side wall of the GaN mesa is smooth, the edge is flat, there is no etching damage, and the mask part (SiO 2 dielectric layer) essentially no GaN deposition.

[0055] It can be seen from the above examples that the method provided by the present invention can directly grow patterned GaN on the sapphire template, and directly obtain the required shape of the GaN mesa without etching the GaN layer, and the obtained device has no etching damage and will not cause device performance to degrade.

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com