Method and device for confirming physical location of failure address in chip storage area

A technology of physical location and storage area, which is applied in the field of confirming the physical location of failure addresses in chip storage areas, and can solve problems such as limited accuracy of physical location, failure, and bad analysis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] As mentioned in the background art, the accuracy of the physical location of the failed storage unit found by the existing method is limited, which easily leads to failure of bad analysis.

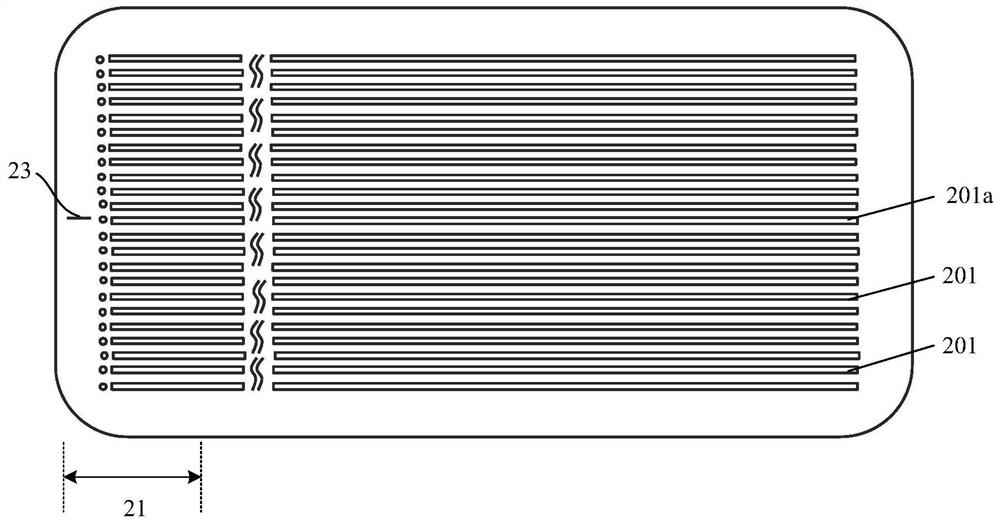

[0045] The study found that the failed row address is generally distinguished at the edge of the storage area, and then moved in parallel to the corresponding failed column address in the electron microscope equipment, and finally the physical address of the failed memory unit is found and marked for slice analysis. However, when the target area is far from the edge of the storage area, the stage of the electron microscope equipment needs to be moved for a long distance, and the long-distance movement of the electron microscope equipment stage is prone to deviation, resulting in incorrect addresses and analysis failures.

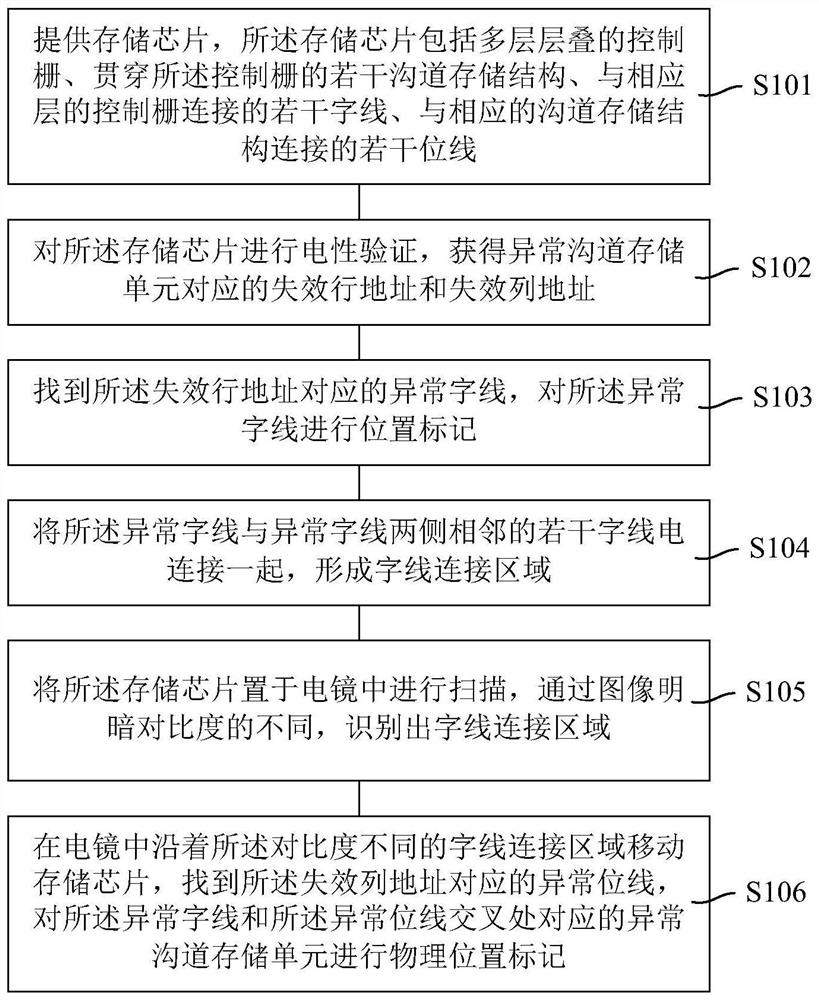

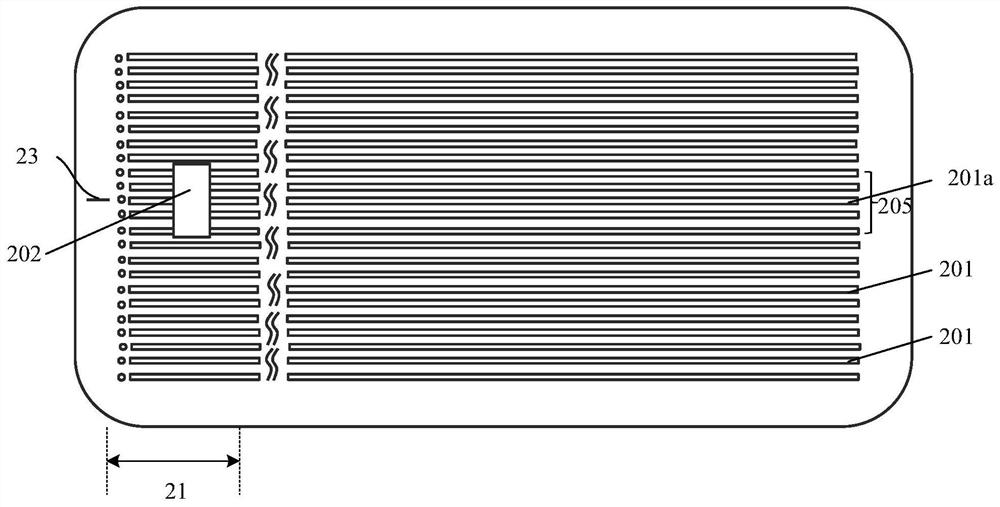

[0046] To this end, the present invention provides a method and device for confirming the physical location of a failure address in a chip storage area of the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com