Capacitor array switching method applied to low-voltage SAR ADC

A capacitor array, ADC1 technology, applied in the field of capacitive DAC, can solve the problems of difficult high-quality transmission of the third level, low power supply voltage, and the loss outweighs the gain.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The embodiments of the present invention will be described below in conjunction with the accompanying drawings of the specification.

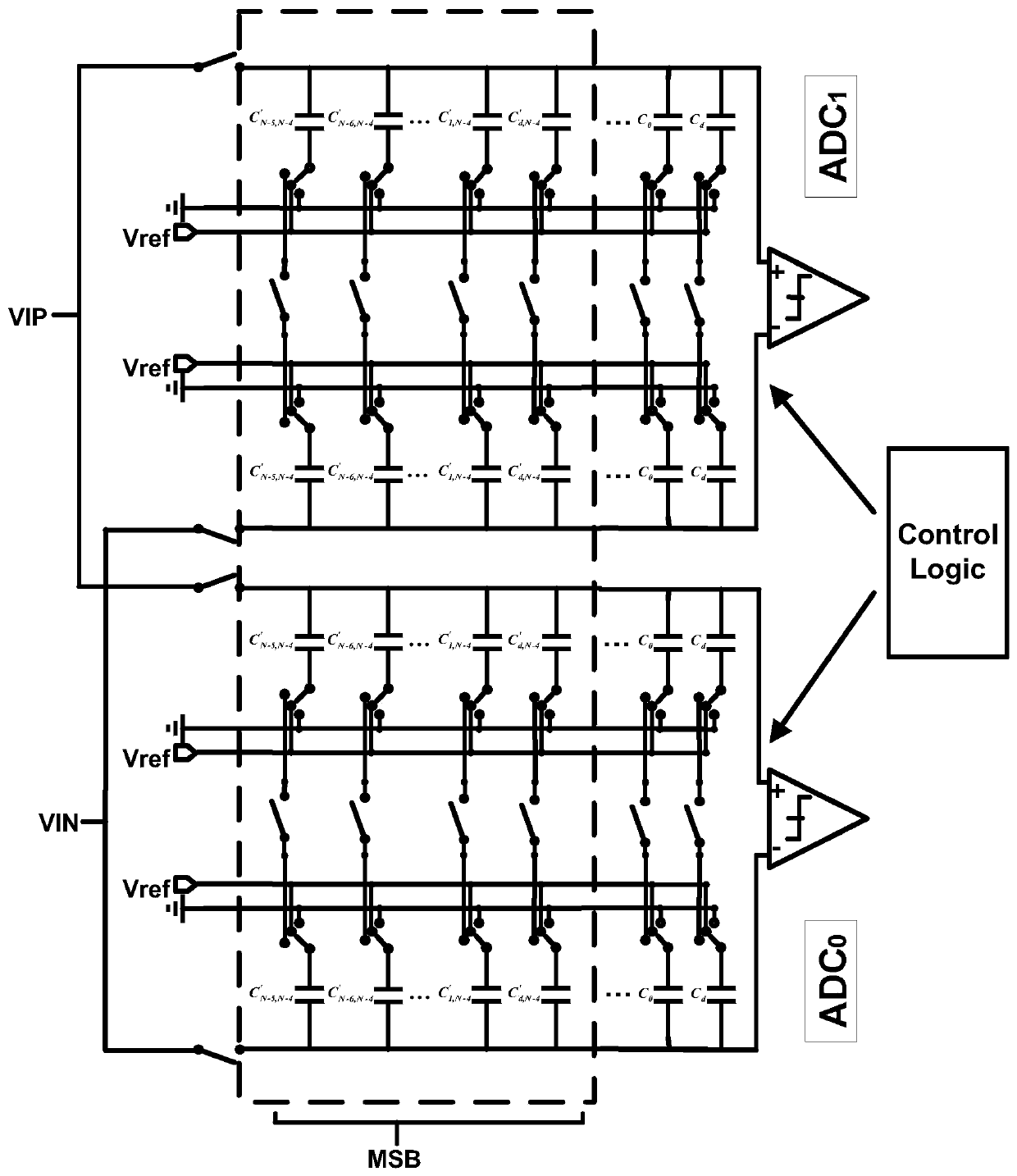

[0045] The present invention designs a capacitor array switching method applied to low-voltage SAR ADC. The analog-to-digital converter based on the method includes two SAR ADCs with exactly the same structure, that is, two N-bit sub-analog-to-digital converter ADCs. 0 And ADC 1 , And the structure of a single N-bit SAR ADC is as figure 1 As shown, ADC 0 And ADC 1 Each includes a sampling switch, a capacitor array, a comparator, and digital control logic, where the capacitor array includes an identical upper capacitor array and a lower capacitor array; the ADC 0 And ADC 1 In, the input signal VIP is connected to the top plate of the upper capacitor array through the sampling switch, and the input signal VIN is connected to the top plate of the lower capacitor array through the sampling switch; the top plate of the upper capacitor array is con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com