Decoding method based on dvb-s2 standard ldpc code parallel decoding fpga implementation architecture

A technology of DVB-S2 and LDPC codes, applied in the field of FPGA technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

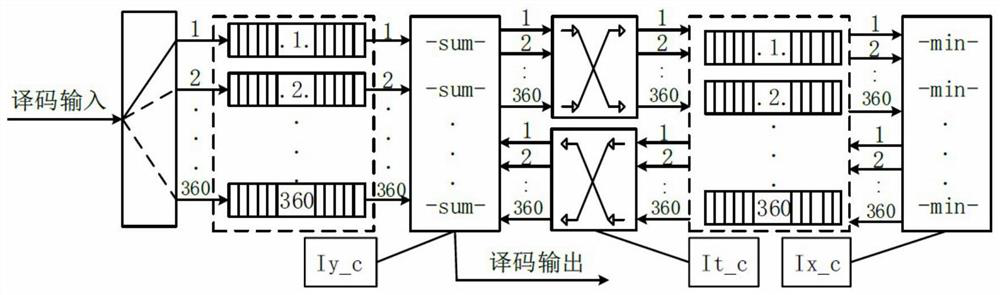

[0033] Such as figure 1 As shown, the FPGA implementation method of IRA-LDPC code parallel decoding based on DVB-S2 standard designed in this paper mainly includes the following parts: serial-to-parallel conversion (S2P), input buffer (RAM_L), variable node update (VPR), interleaving It is composed of six parts including device (It), node cache (RAM_P) and check node update (SPR).

[0034] (1) Serial-to-parallel conversion (S2P). Parallel storage control is performed on the serial decoding input. The front system codes are stored in parallel in 360 input buffers (RAM_L) in sequence, and the check codes are stored in serial in 360 input buffers (RAM_L) in sequence.

[0035] (2) Input cache (RAM_L). Consists of 360 independent memories (RAM), single input and single output, storing decoding input (likelihood ratio), and the storage depth of each memory is the code length divided by 360.

[0036] (3) Variable node update (VPR). It consists of 360 independent variable node upd...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com