Laminated structure for three-dimensional memory, three-dimensional memory and preparation method thereof

A technology of stack structure and memory, applied in semiconductor devices, electric solid state devices, electrical components, etc., can solve the problems of wide threshold voltage distribution of three-dimensional memory, fast programming/erasing speed, serious memory cell read interference, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

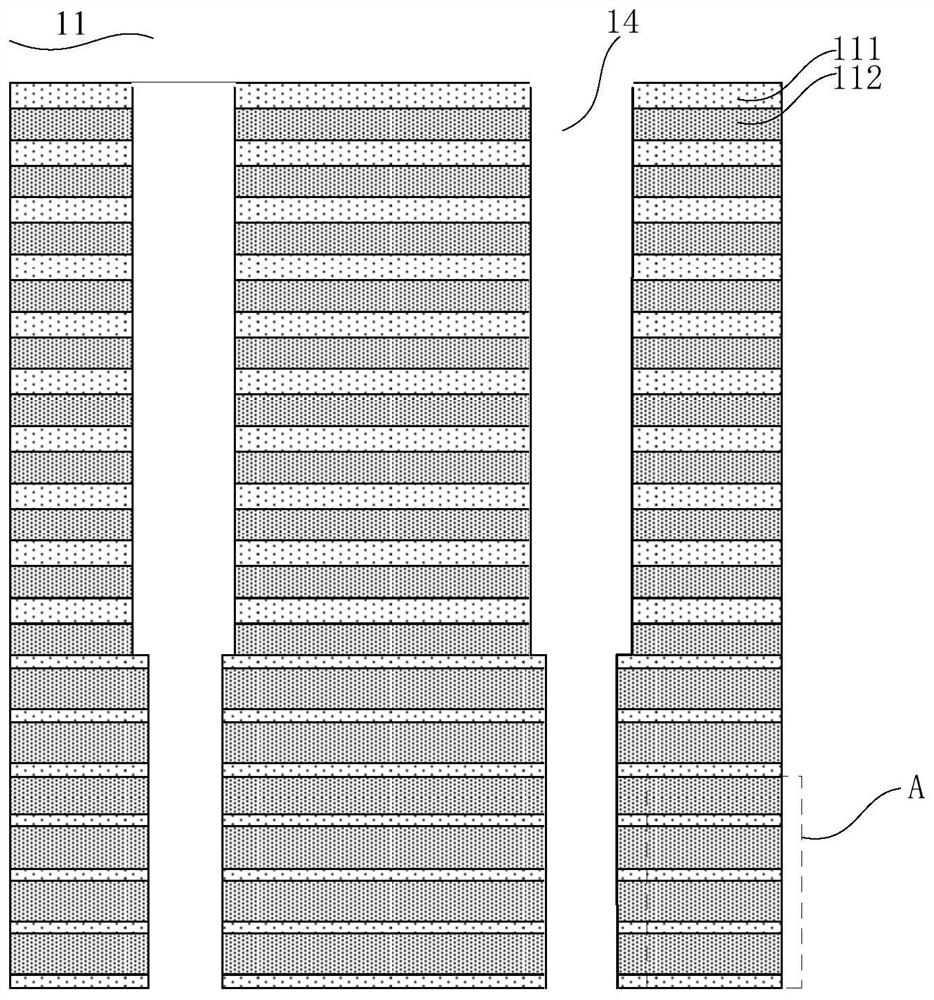

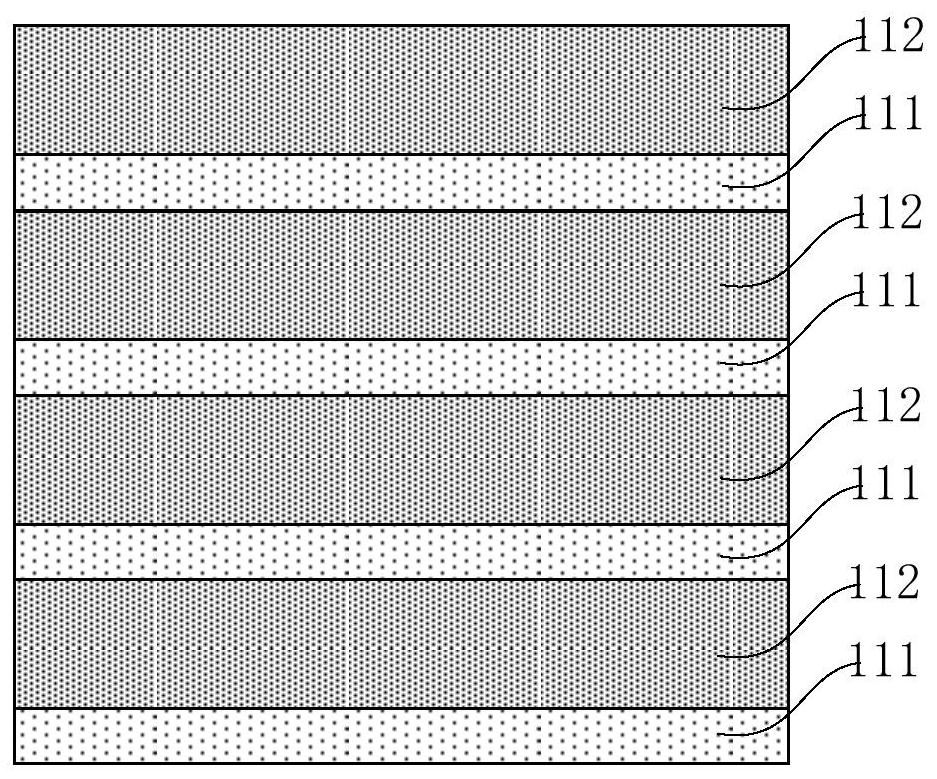

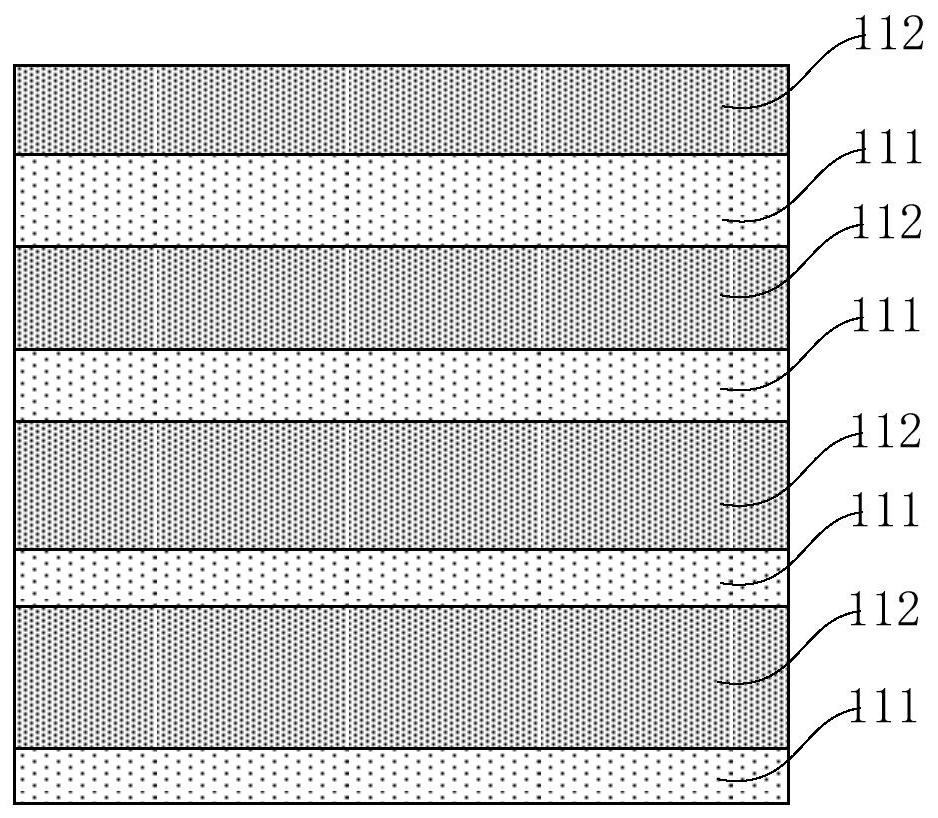

[0115] see figure 1 , the present invention provides a stacked structure 11 for a three-dimensional memory, the stacked structure 11 for a three-dimensional memory includes sacrificial layers and inter-gate dielectric layers alternately stacked up and down; the stacked structure 11 is formed with Along the thickness direction of the stacked structure 11, the channel via hole 14 passing through the stacked structure 11, along the thickness direction of the stacked structure 11, the width of each part of the channel via hole 14 is not the same; The thickness of the sacrificial layer 111 is directly proportional to the width of the channel via 14 and the thickness of the inter-gate dielectric layer 112 is inversely proportional to the width of the channel via 14 .

[0116] As an example, the laminated structure 11 can be divided into an upper part and a lower part from top to bottom along the thickness direction of the laminated structure 11, and the ratio of the upper part of th...

Embodiment 2

[0138] see Figure 11 The present invention provides a stacked structure 12 for a three-dimensional memory, the stacked structure 12 for a three-dimensional memory includes sacrificial layers and inter-gate dielectric layers alternately stacked up and down; the stacked structure 12 is formed with Along the thickness direction of the stacked structure 12, the channel via hole 14 passing through the stacked structure 12, along the thickness direction of the stacked structure 12, the width of each part of the channel via hole 14 is not the same; The thickness of the gate layer 121 is directly proportional to the width of the channel via 14 and the thickness of the inter-gate dielectric layer 112 is inversely proportional to the width of the channel via 14 .

[0139] As an example, the laminated structure 12 can be divided into an upper part and a lower part from top to bottom along the thickness direction of the laminated structure 12, and the ratio of the upper part of the lamin...

Embodiment 3

[0161] see Figure 21 , the present invention also provides a method for preparing a three-dimensional memory, the method for preparing a three-dimensional memory includes the following steps:

[0162] 1) Provide a semiconductor substrate;

[0163] 2) forming a stacked structure as described in Embodiment 1 on the semiconductor substrate;

[0164] 3) forming an epitaxial layer at the bottom of the channel via hole;

[0165] 4) forming a functional sidewall on the sidewall of the channel via hole, and forming a channel layer on the surface of the functional sidewall and the upper surface of the epitaxial layer;

[0166] 5) forming a gate gap in the stacked structure;

[0167] 6) removing the sacrificial layer based on the gate gap to form a sacrificial gap; and

[0168] 7) Forming a gate layer in the sacrificial gap.

[0169] In step 1), see Figure 21 Step S1 in and Figure 22 , providing a semiconductor substrate 13 .

[0170] As an example, the semiconductor substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com