Positive temperature coefficient polycrystalline silicon resistor structure and manufacturing method thereof

A technology of polysilicon resistance and positive temperature coefficient, which is applied in the direction of resistors, circuits, electrical components, etc., can solve the problems of inability to obtain polysilicon resistance structure design and limitations, and achieve the effect of avoiding performance limitations and excellent process stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention is described in detail below in conjunction with accompanying drawing:

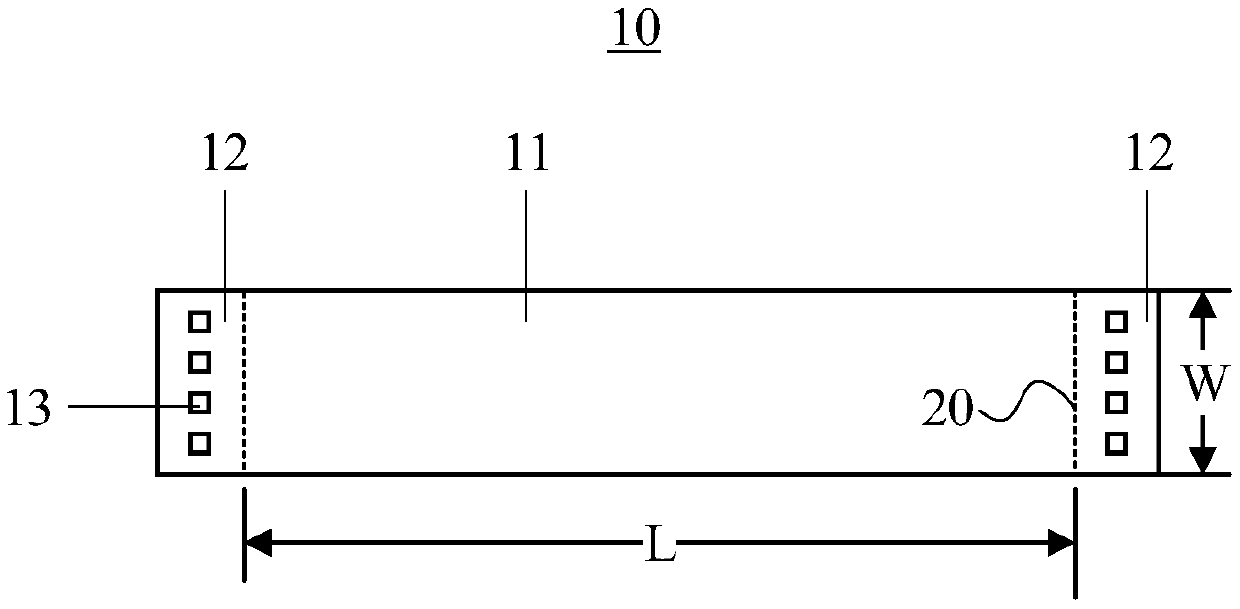

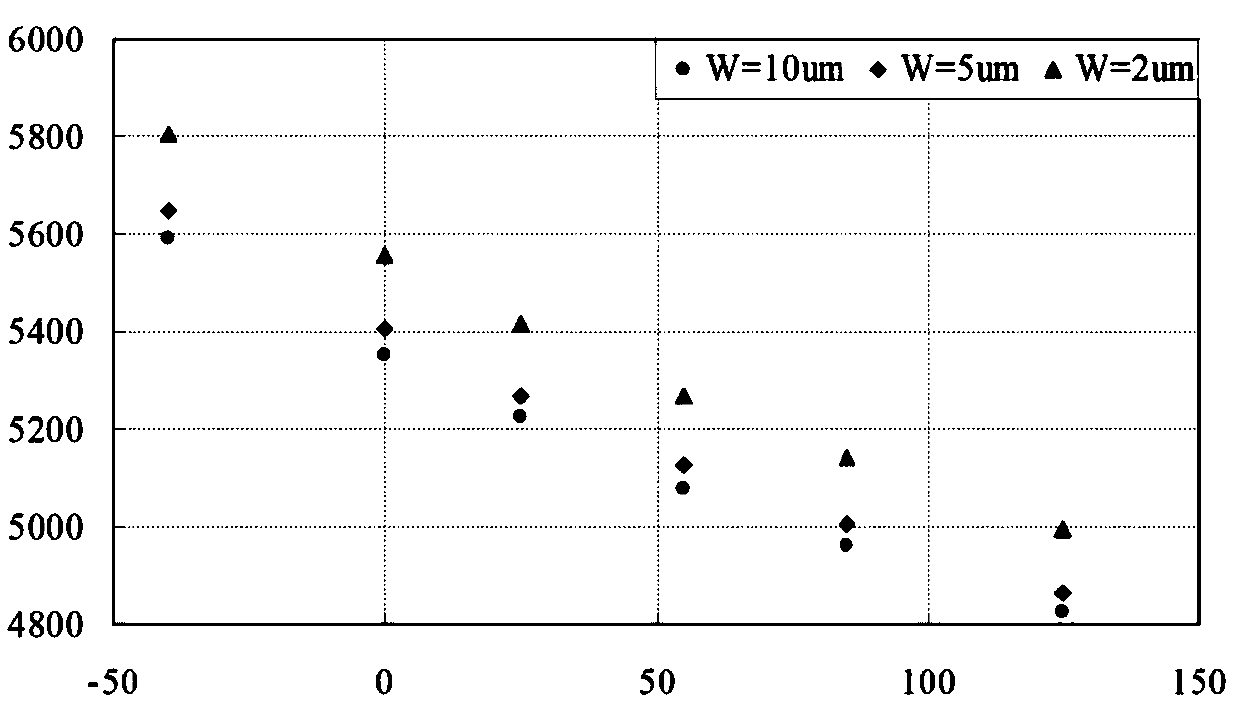

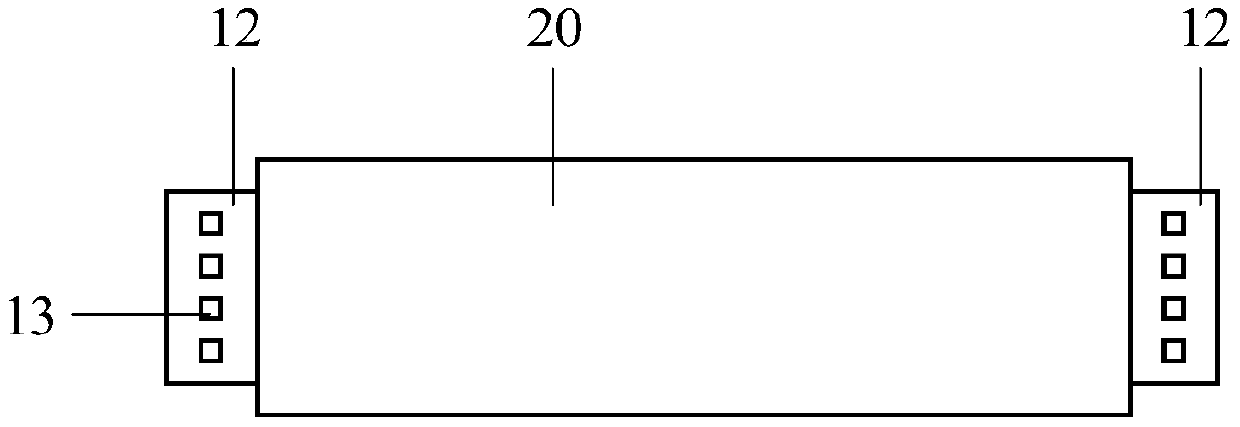

[0024] image 3 It is a structural schematic diagram of covering a metal silicide barrier layer in the middle area of a traditional non-metallized polysilicon resistor. Please refer to image 3 , due to the polysilicon resistance structure in the manufacturing process, by setting the metal silicide barrier layer 20 in the middle region 11 to prevent the metallization of the middle region 11, and the exposed end region 12 is generally provided with a contact hole 13 through the metal silicide metal After melting, they are connected by metal wires to form a polysilicon resistance structure with a negative temperature change in resistance value. Figure 4 is a curve diagram of the resistance value of the middle region of the polysilicon resistance structure changing with temperature; Figure 5 It is a graph showing the variation of resistance value with temperature after the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com