A debugging system of fpga parameters based on hardware-in-the-loop simulation

A semi-physical simulation and parameter debugging technology, which is applied in transmission systems, transmission monitoring, electrical components, etc., can solve the problem of lengthy and time-consuming FPGA loop parameter debugging process, reduce the number of parameter debugging times, shorten the debugging time, compile less frequent effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Specific embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0035] The parameter debugging system method of the present invention can realize the generation of real signals according to the communication link parameters obtained by simulation, receive signals through a signal processing receiver, and realize online debugging of FPGA loop parameters through an intelligent controller.

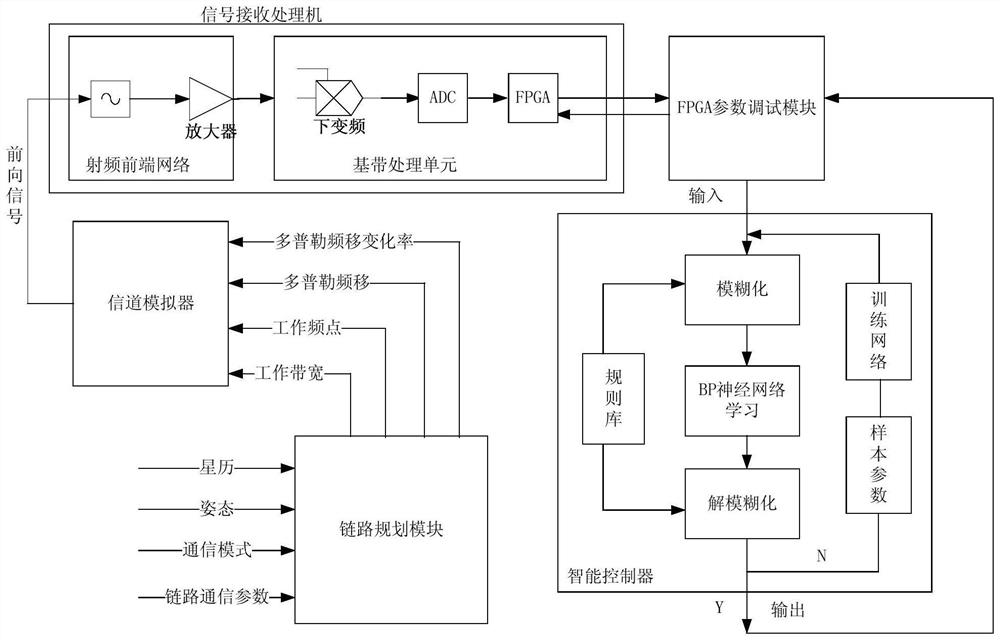

[0036] Such as figure 1 As shown, the present invention proposes a kind of FPGA parameter debugging system based on hardware-in-the-loop simulation, it is characterized in that comprising: link planning module, channel simulator, signal receiving processor, intelligent controller and FPGA debugging module;

[0037] The link planning module calculates the link planning simulation results through the external input of the aircraft's ephemeris, attitude, communication mode and link communication parameters and provid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com