A high-speed cache device and a data high-speed read-write terminal

A high-speed cache and memory technology, which is applied in the field of high-speed cache devices and high-speed data read-write terminals, can solve the problems of low integration, small capacity, and incompatibility with QDRSRAM memory, etc., and achieve high access efficiency and low modification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

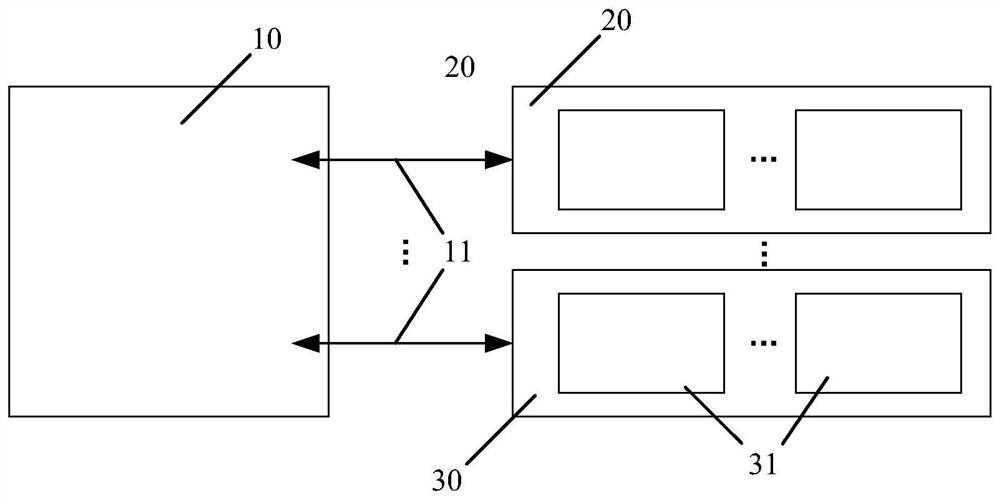

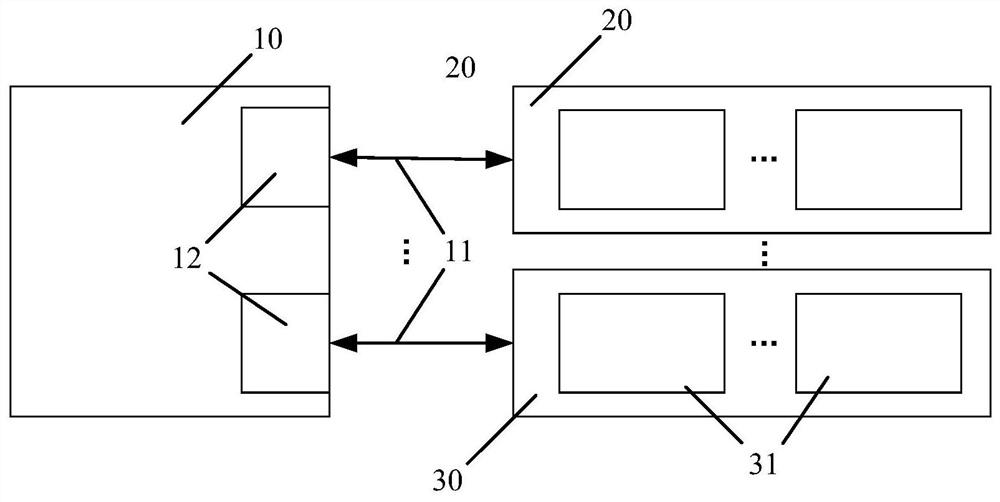

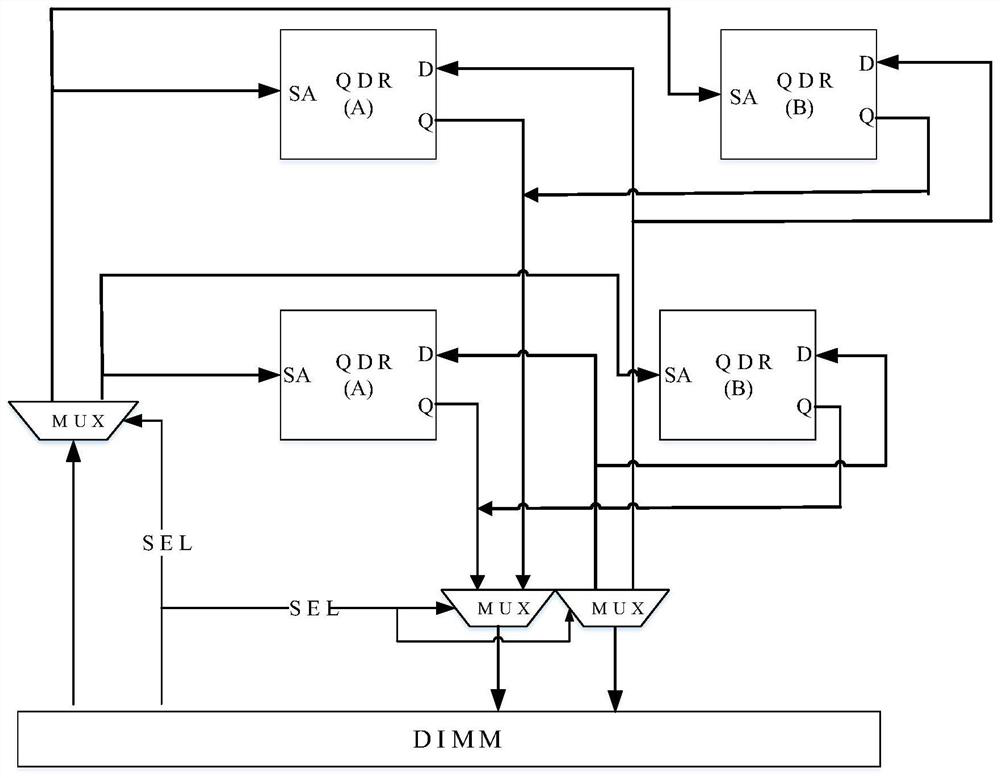

[0027] The core of this application is to provide a high-speed cache device composed of a processor motherboard, DDR SDRAM and QDR SRAM and a high-speed data read-write terminal provided with the cache device, and the QDR SRAM particles are packaged based on the DIMM interface adopted by conventional DDRSDRAM The obtained QDR SRAM can be directly connected to the processor main board through the existing DIMM interface of the processor. This is because the difference in random address access efficiency between QDR SRAM and DDR SDRAM is not directly related to the interface type and will not affect QDR SRAM has high access efficiency characteristics, and because it does not need to replace the interface type on the processor motherboard, it can bring higher access efficiency with a lower degree of modification, meeting the needs of special application scenarios such as banks.

[0028] In order to make the purposes, technical solutions and advantages of the embodiments of the pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com