A FPGA/IP core logic code security rule detection method

A rule and code technology, applied in the field of FPGA/IP core logic code security rule detection, can solve problems such as lack of security rule sets, and achieve the effect of reducing invalid warning rules and improving quality.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] In order to make the purpose, content, and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

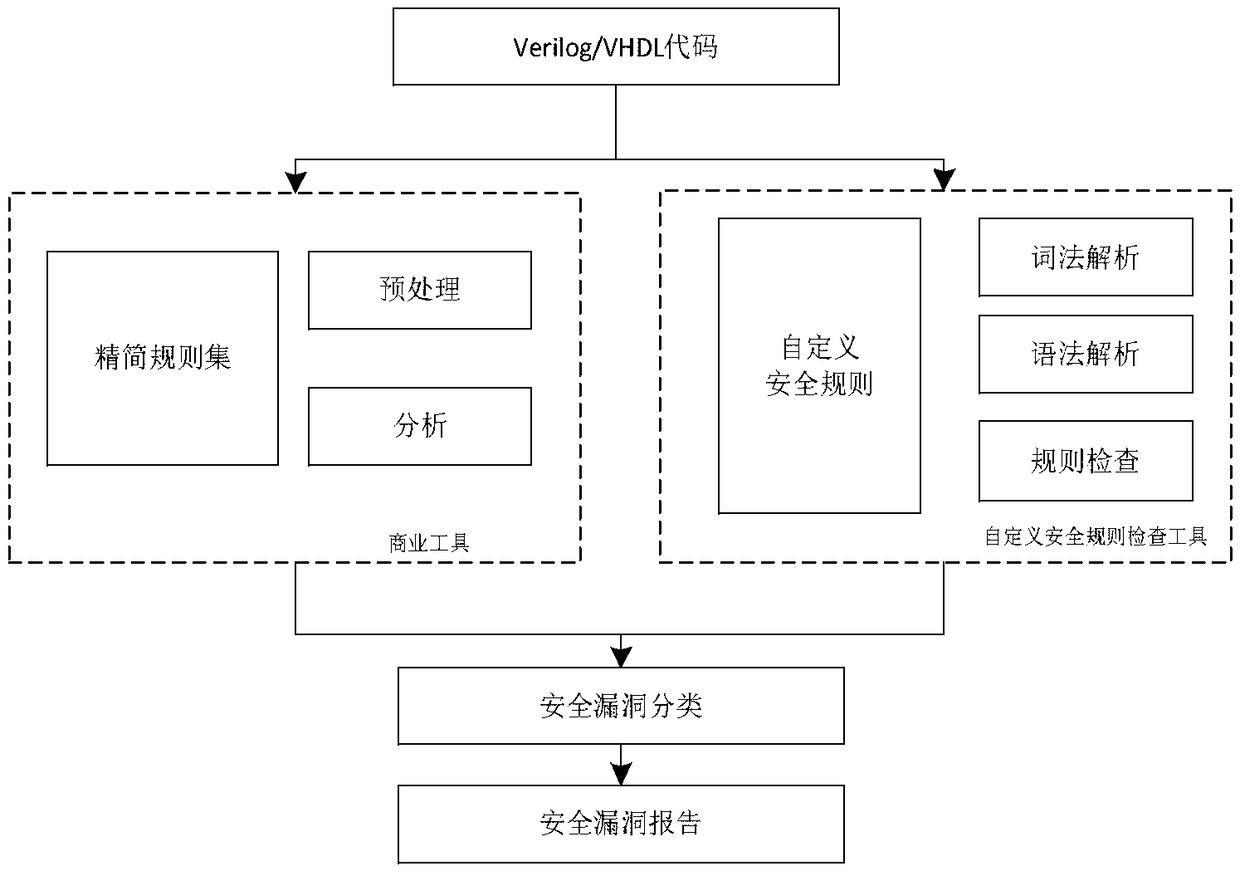

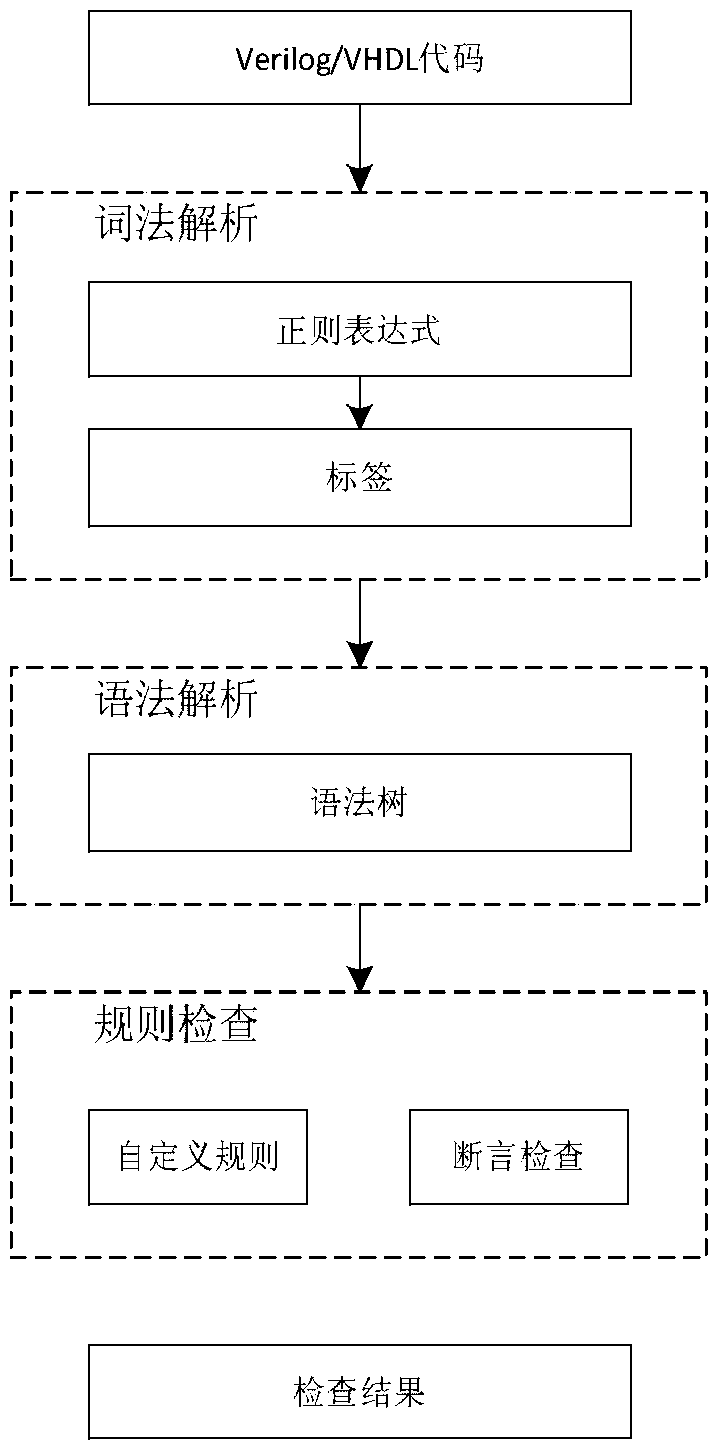

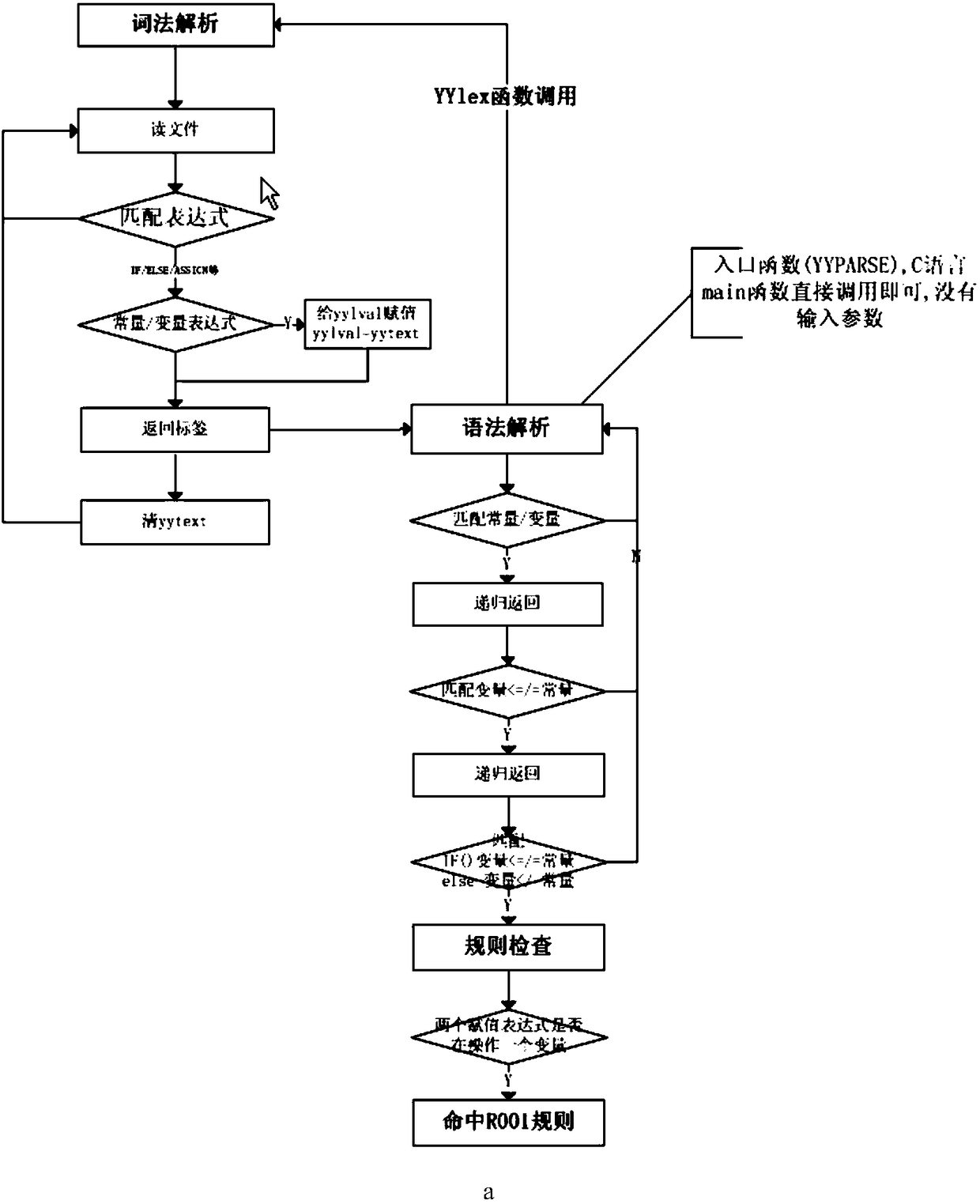

[0052] Aiming at the problem that the current static rule detection method lacks a subset of programmable device security rules, the present invention proposes a relatively complete set of comprehensive rule detection methods, which can be applied to the logic code security rule detection of FPGA / IP cores, and effectively detect FPGA or The standardization of the RTL code of the IP core. Such as figure 1 Shown, FPGA / IP core logic code security rule detection method of the present invention comprises the following steps:

[0053] Step 1: Input the Verilog HDL code of the FPGA to be verified and use commercial tools (such as LEDA, Alint, Autocheck) to perform routine rule detection, and obtain the routine rule detection...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com