A double-sided three-dimensional stacked packaging structure and packaging method

A three-dimensional stacking and packaging structure technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve problems such as component warpage, and achieve the effect of reducing the occupied area and improving the utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

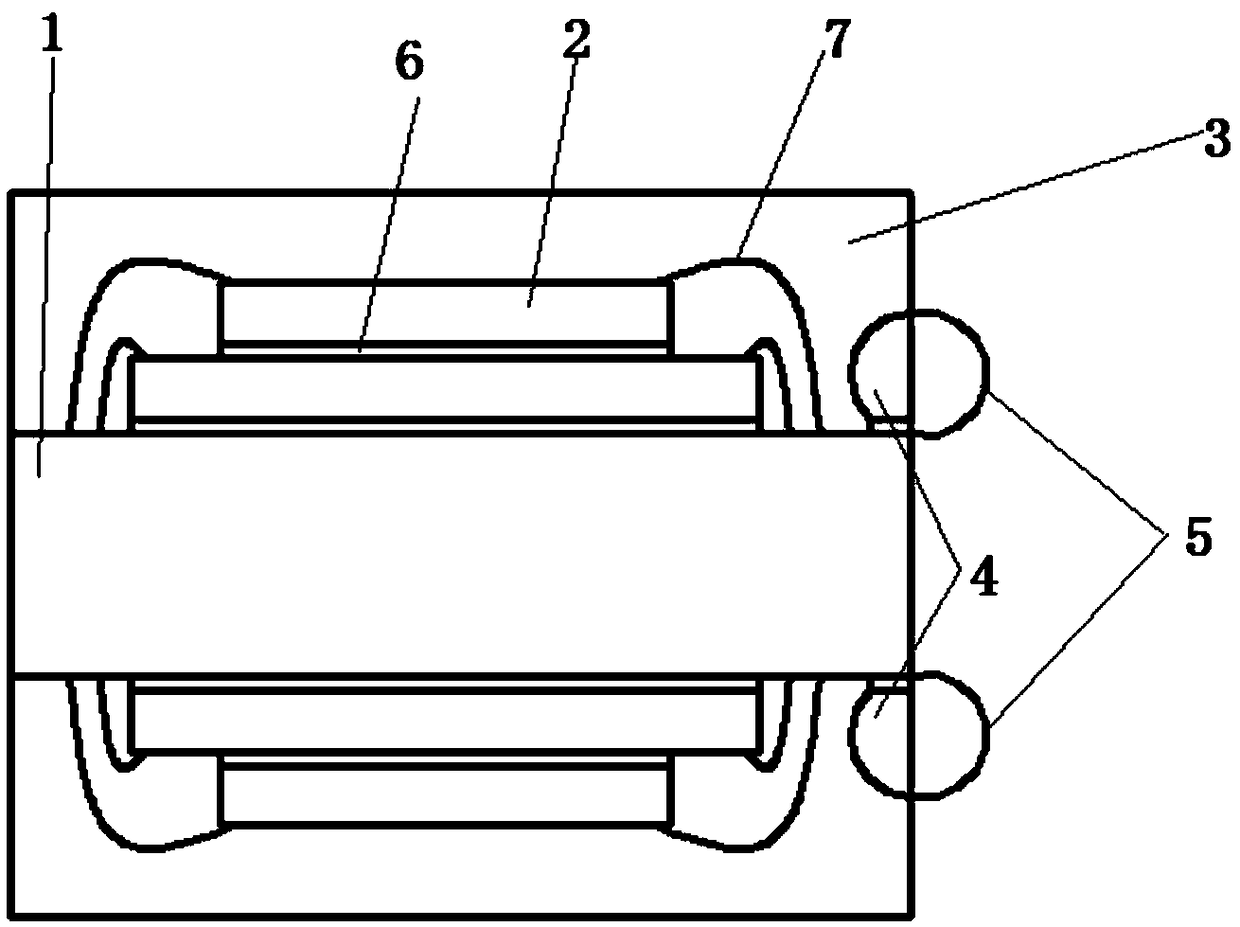

[0033] An embodiment of the present invention provides a double-sided three-dimensional stack package structure, such as figure 1 As shown, the double-sided three-dimensional stack package structure includes: a substrate 1 and a chip 2, at least one layer of chips 2 are respectively stacked on the first surface and the second surface of the substrate 1, and the chip 2 is electrically interconnected with the substrate 1; The chip 2 is encapsulated by a plastic encapsulation material 3 to form a package structure.

[0034] In the embodiment of the present invention, the substrate 1 is provided with wiring, and the chip 2 is electrically interconnected with the substrate 1 through the bonding wire 7. The bonding wire 7 is a gold wire with a diameter of 20um. The bonding wire is selected from a gold wire because it has a large electrical conductivity. , corrosion resistance, good toughness advantages. But it is not limited thereto. In other embodiments, the welding wire 7 can be ...

Embodiment 2

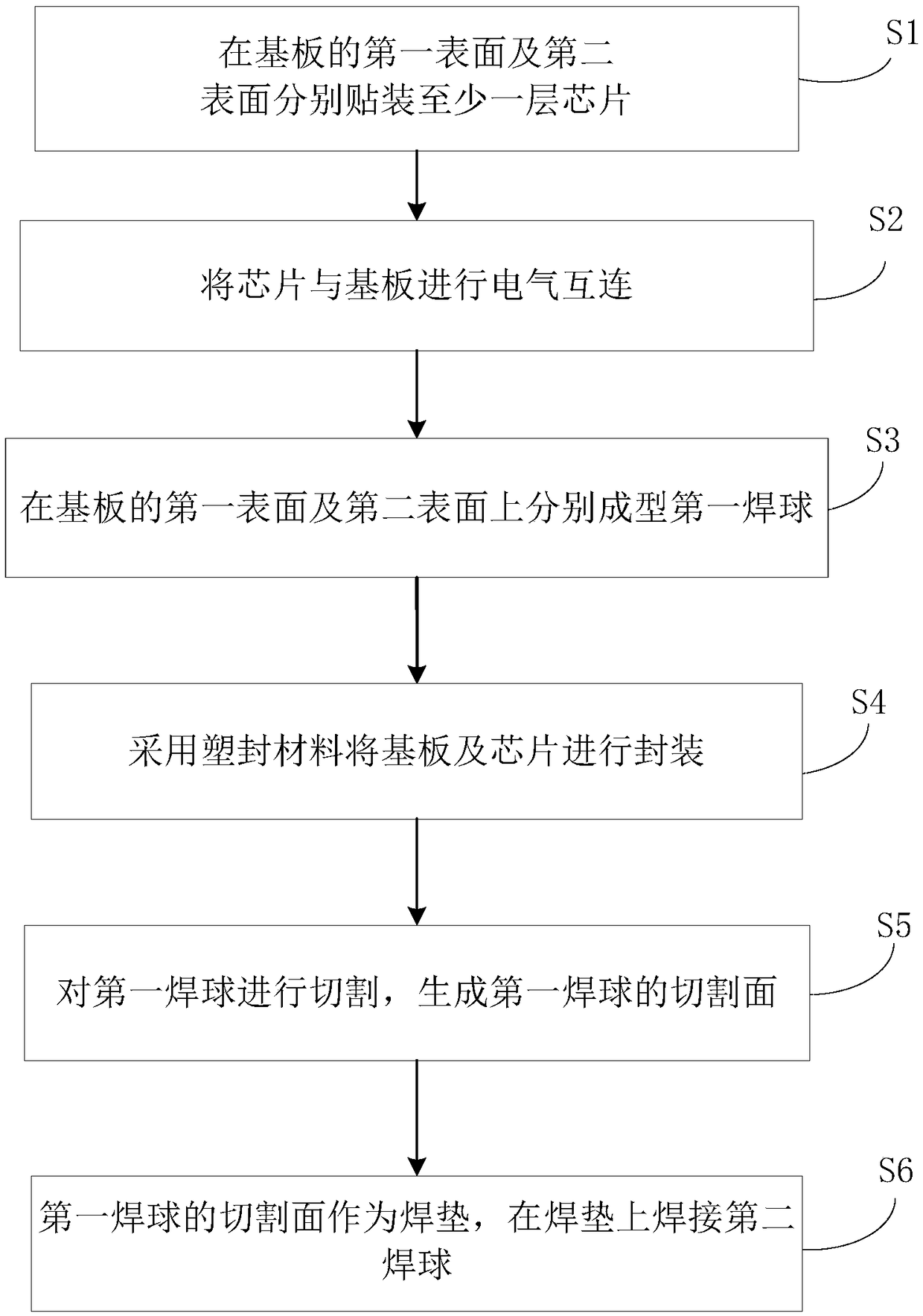

[0040] An embodiment of the present invention provides a double-sided three-dimensional stack packaging method, such as figure 2 As shown, the double-sided three-dimensional stack packaging method includes the following steps:

[0041] Step S1: mounting at least one layer of chips on the first surface and the second surface of the substrate respectively.

[0042] In a preferred embodiment, the same number of chips are mounted symmetrically on the first surface and the second surface of the substrate, so as to reduce or avoid the problem of warpage after plastic packaging caused by mismatching thermal expansion systems of different materials.

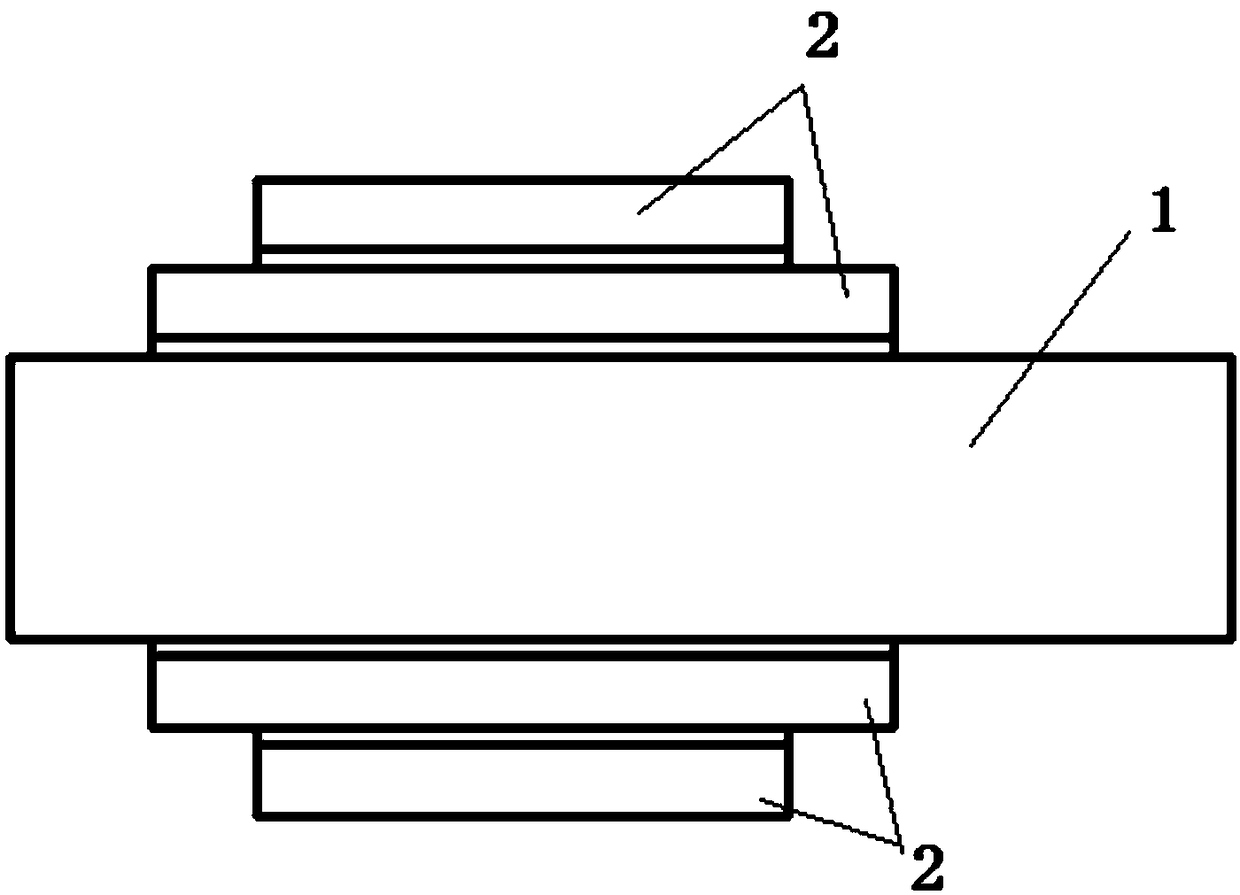

[0043] In the embodiment of the present invention, such as image 3 As shown, two layers of chips 2 are mounted symmetrically on the first surface and the second surface of the substrate 1 . But it is not limited thereto. In other embodiments, different numbers of chips can be mounted on the first surface and the second surface of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com