A pre-compression method and system for integrated circuit layout planning

An integrated circuit and pre-compression technology, which is applied in the fields of electrical digital data processing, instruments, computing, etc., can solve problems such as increasing production costs, reducing work efficiency, and increasing circuit layout area, so as to reduce production costs and improve utilization. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

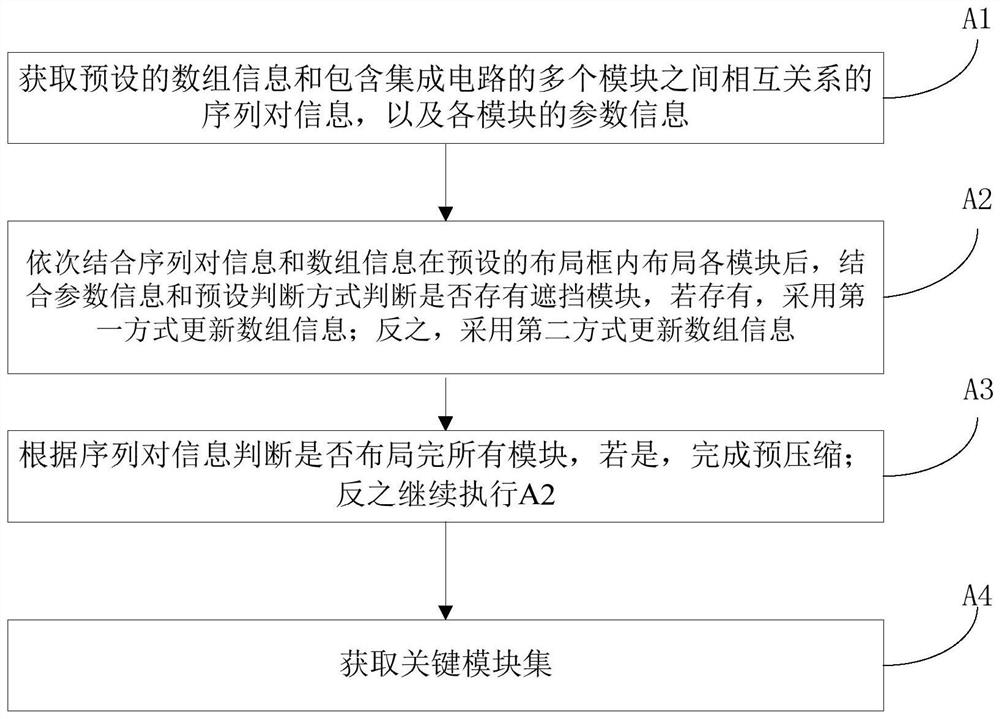

[0054] like figure 1 As shown, a pre-compression method for integrated circuit layout planning includes the following steps:

[0055] A1. Acquire preset array information, sequence pair information about the relationship between multiple modules including an integrated circuit, and parameter information of each module. The parameter information is length information, width information, area information and type information of the module.

[0056] A2. After arranging each module in the preset layout frame by combining the sequence pair information and the array information in turn, combine the parameter information and the preset judgment method to determine whether there is an occlusion module. If there is, use the first method to update the array information; otherwise , using the second method to update the array information. The array information includes parameter information of the left border of the layout frame, parameter information of the lower border of the layout...

specific Embodiment 1

[0073] Combine below Figure 2 to Figure 14 The above method is explained in detail.

[0074] Assuming that the integrated circuit contains six modules, the numbers of the six modules are respectively abcdef, and their sizes are shown in Table 1.

[0075] Table 1

[0076] module a module b module c module d module e module f width 8 6 3 5 7 3 high 4 3 5 5 6 7

[0077] Also assume that the sequence pairs for this circuit layout are as follows.

[0078]

[0079] Set an array en, which stores: the left border of the circuit layout box, represented by the letter l; the lower border of the circuit layout box, represented by the letter s; and the number of the module.

[0080] First, put l and s in the positive sequence respectively the beginning and end of the

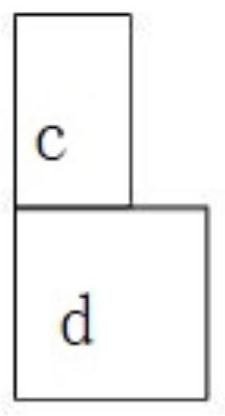

[0081] The first module in the reverse sequence is module d, and the sequence pair is According to the sequence pair properties, module d will be located in X 1 ...

Embodiment 2

[0099] A pre-compression system for integrated circuit layout planning, comprising:

[0100] a memory for storing at least one program;

[0101] The processor is configured to load the at least one program to execute the pre-compression method for layout planning of an integrated circuit described in any one of the above.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com