A lateral semiconductor device with a shallow trench isolation structure interlaced with interdigitated arrangement

A lateral semiconductor, shallow trench isolation technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of increased device on-resistance, inability to achieve compromise, and increased flow paths, reducing Small surface electric field, reduced impact ionization rate, and uniform electric field distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

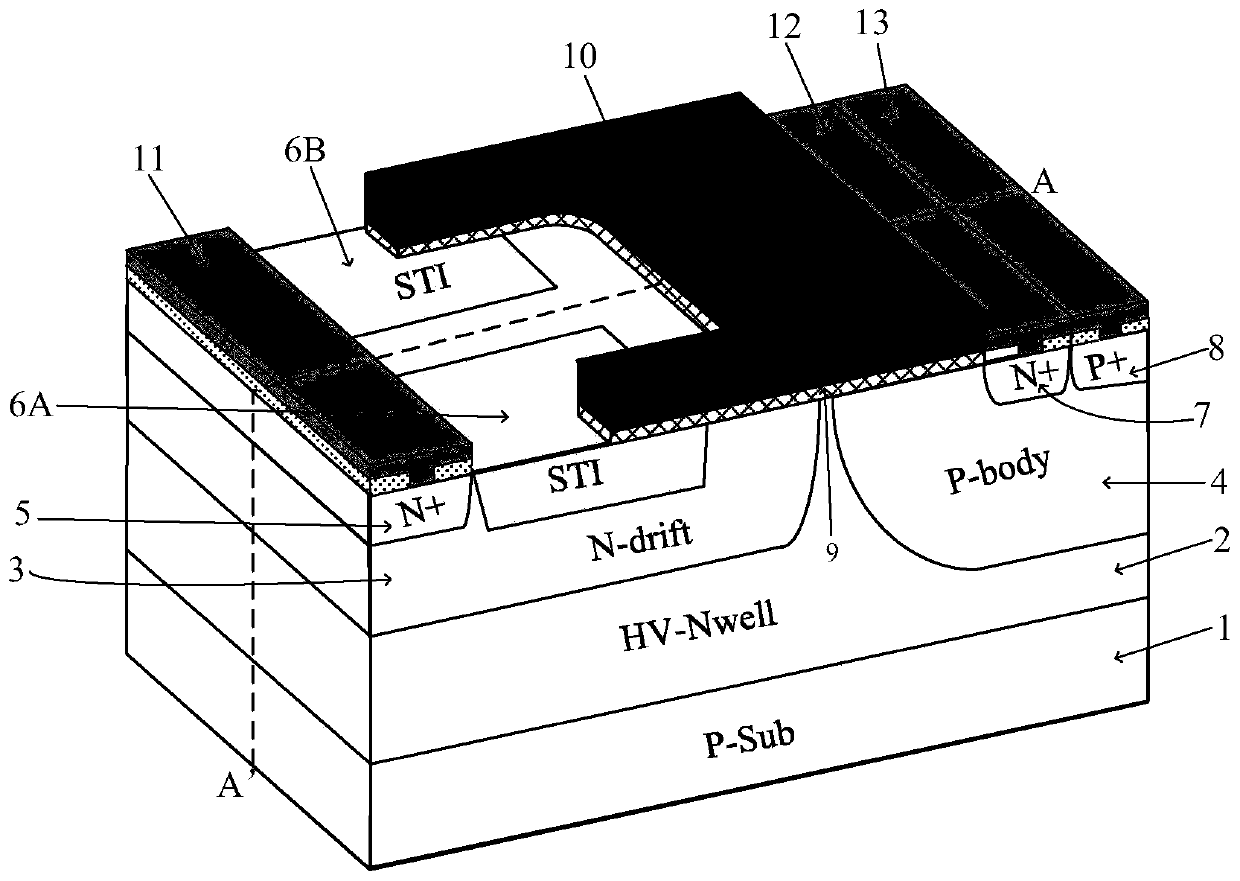

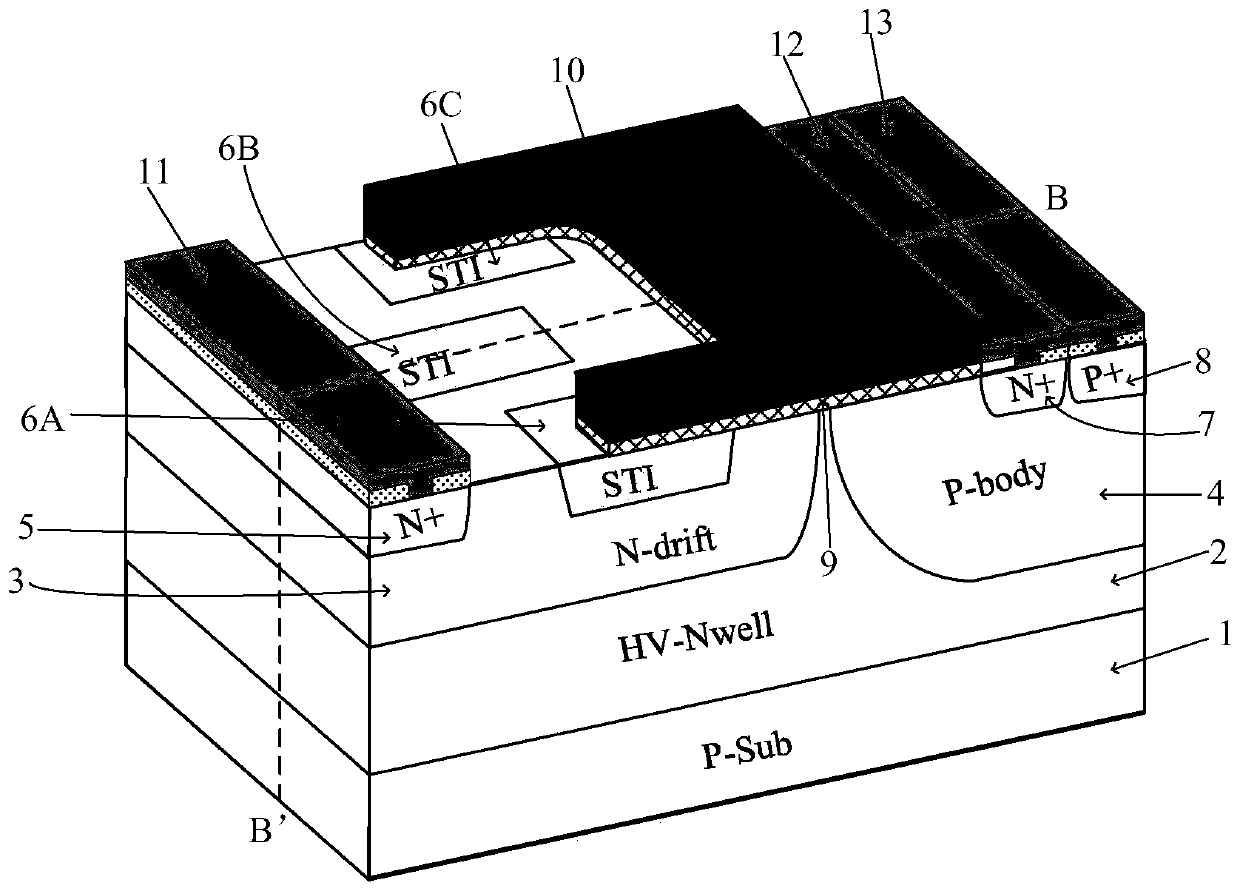

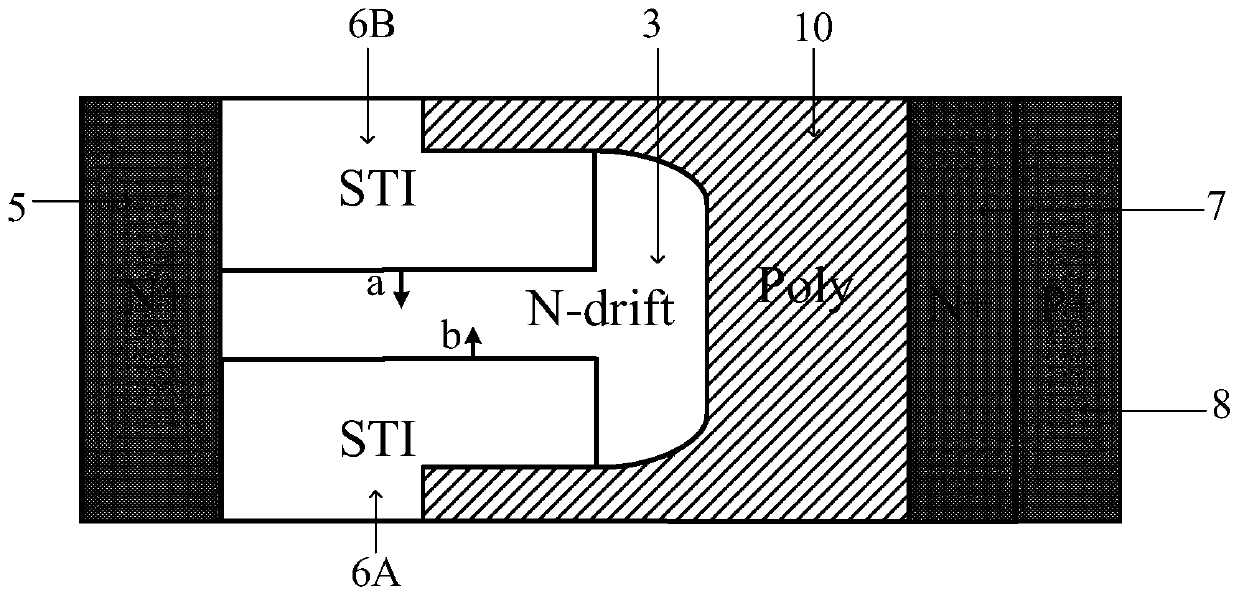

[0019] A lateral semiconductor device with an interdigitated shallow trench isolation structure, comprising: a P-type substrate 1, a high-voltage N-type region 2 is arranged above the P-type substrate 1, and a high-voltage N-type region 2 is arranged above the high-voltage N-type region 2. The N-type drift region 3 and the P-type body region 4 are provided with an N-type drain region 5, a first shallow trench isolation region 6A, a second shallow trench isolation region 6B and a third shallow trench isolation region 6C in the N-type drift region 3 In the P-type body region 4, an N-type source region 7 and a P-type region 8 are arranged, and a U-shaped gate oxide layer 9 is also arranged on the high-voltage N-type region 2, and the U-shaped opening of the gate oxide layer 9 faces the drain and both ends extend to the top of the P-type body region 4 and the top of the first shallow trench isolation region 6A and the third shallow trench isolation region 6C, and a polysilicon gate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com