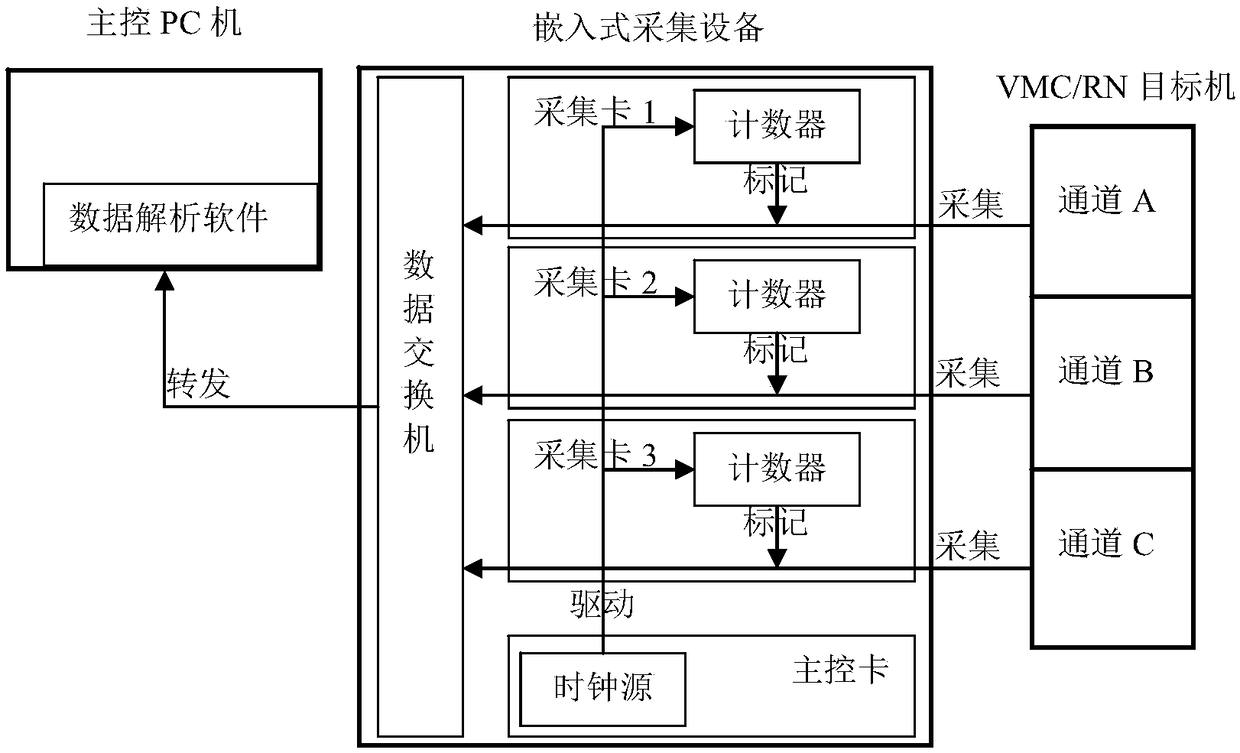

Time mark alignment method for redundancy system data acquisition

A technology of system data and redundancy, applied in general control systems, control/regulation systems, instruments, etc., can solve problems such as low time stamp accuracy, out-of-step, and influence on data analysis effects, so as to ensure real-time performance and accuracy, Improved reliability, easy-to-achieve effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0016] Example 1: Resynchronization test of each redundant channel after VMC restarts 1

[0017] The embedded acquisition device chooses to observe the heartbeat value of the VMC operating system. After starting data acquisition, power off all channels of VMC, and then power on VMC A, B, and C in turn (within 3 seconds). After stopping the acquisition, use the data analysis software to draw The heartbeat value of the operating system. After confirming the asynchronous power-on operation of the VMC, the on-board software starts synchronization, and the heartbeat value of the three-channel VMC restarts to increase synchronously.

[0018] Because the present invention is realized based on CPLD / FPGA hardware resources and embedded real-time software in the embedded acquisition device, it effectively avoids the limitations of using the target machine to generate time stamps and must ensure the synchronization of the target machine itself.

Embodiment 2

[0019] Example 2: Resynchronization test of each redundant channel after VMC restarts 2

[0020] The embedded acquisition device chooses to observe the heartbeat value of the VMC operating system. After starting data acquisition, power off all channels of VMC, and then power on VMC A, B, and C in turn (interval 5 seconds). After stopping the acquisition, use the data analysis software to draw the operation System heartbeat value, after confirming VMC asynchronous power-on operation, because the asynchronous degree exceeds the on-board software startup synchronization tolerance, the three-channel VMC heartbeat value still increases asynchronously.

[0021] Because the present invention is based on the CPLD / FPGA hardware resources and embedded real-time software in the embedded acquisition device, it effectively avoids using the target machine to generate time scales. When the target machine itself is out of sync, the curve is drawn as three channels synchronously.

Embodiment 3

[0022] Embodiment 3: Mode switching test from VMC PBIT to control management

[0023] The embedded acquisition device selects and observes the VMC operating system system mode word. After starting data acquisition, press the PBIT switch to make VMC enter PBIT, and then press the PBIT switch again to make VMC exit PBIT mode and return to control management mode. After stopping the acquisition, draw with data analysis software The system mode word changes, after confirming that the VMC exits PBIT asynchronously (asynchronously becomes the initialization mode), after the on-board software starts the synchronization, the three-channel VMC system mode word changes to the control management mode at the same time.

[0024] Because the present invention is based on the CPLD / FPGA hardware resources and embedded real-time software in the embedded acquisition device, it effectively avoids the use of the main control PC to generate the time scale, and is subject to the influence of other p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com