Data circular buffering method and device used for SOCFPGA, storage medium and terminal

A circular buffering and data technology, applied in the field of data processing, can solve problems such as the inability to effectively solve the data processing speed mismatch between FPGA and ARM, the impact of data processing efficiency, and the inability to provide data, so as to ensure data integrity, optimize data processing efficiency, The effect of saving system overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

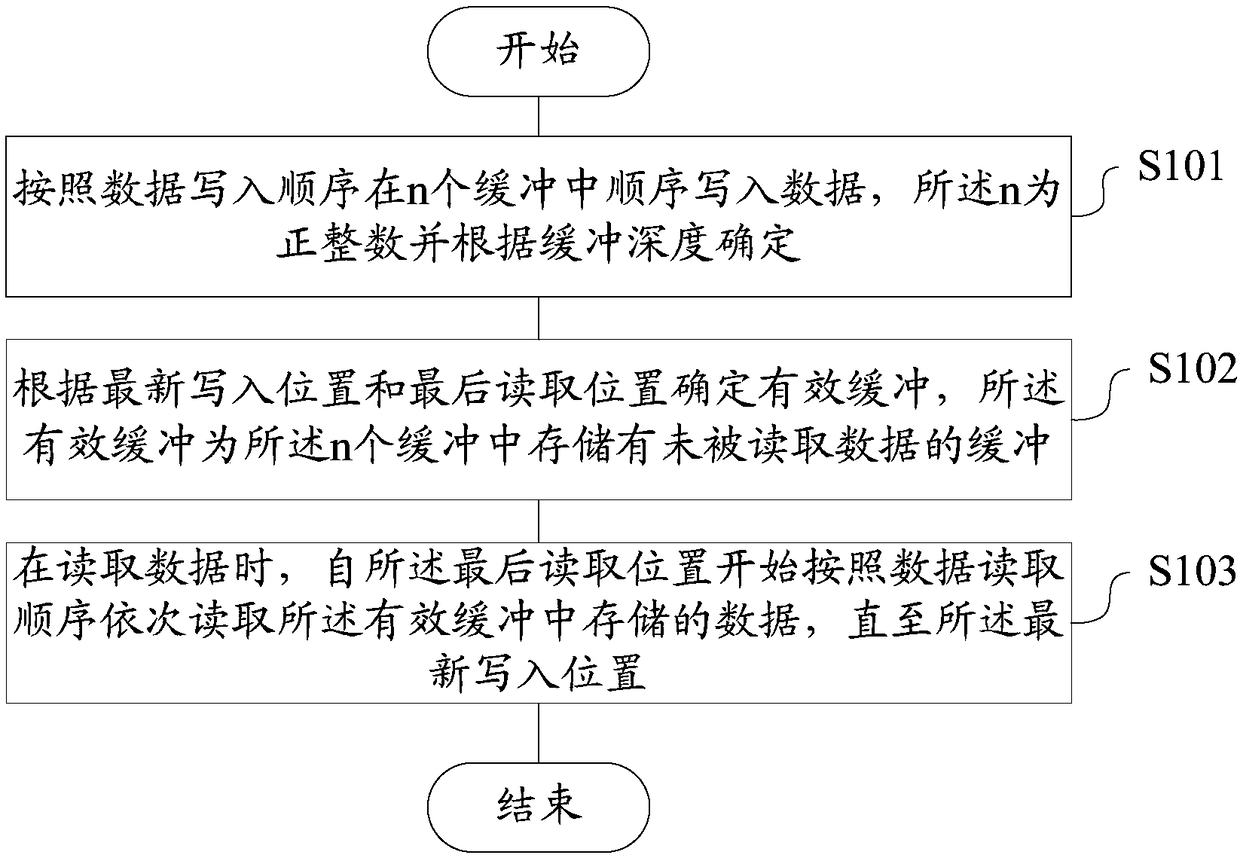

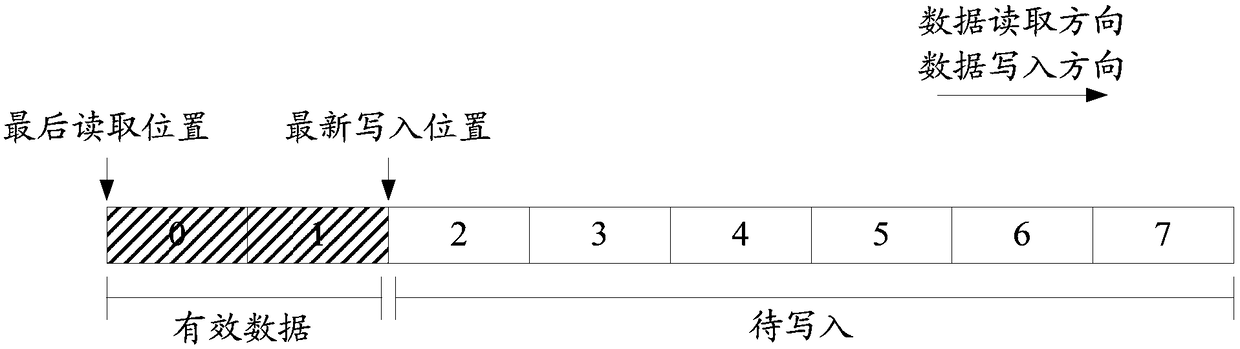

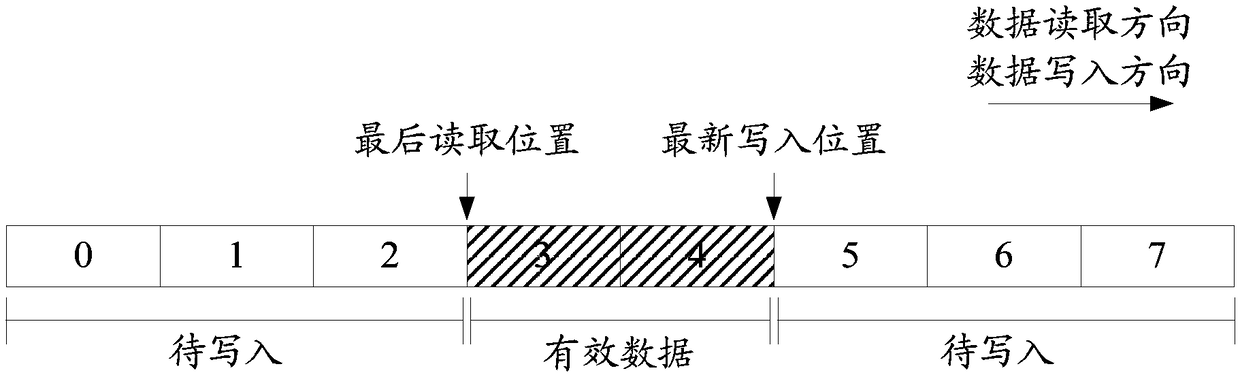

Method used

Image

Examples

Embodiment Construction

[0025] Those skilled in the art understand that, as mentioned in the background art, the data buffering logic of the existing SOCFPGA system still has limitations, which greatly affects the data processing efficiency of the system.

[0026] The inventor finds through analysis that the above-mentioned problem is because the existing SOCFPGA system generally adopts the mode of interrupting and double-buffering to carry out data buffering, to solve the field programmable logic gate array of the enhanced reduced instruction set computer (Advanced RISC Machines, be called for short ARM) (Field Programmable Gate Array, referred to as FPGA) The communication speed does not match the problem.

[0027] However, since there are only two buffers, when the amount of data is large, the central processing unit (Central Processing Unit, referred to as CPU) of ARM is busy, and the time for FPGA and ARM to process data is irregular (such as due to the scheduling relationship of the CPU and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com