Method and device for detecting stability of phase-locked loop output clock signal

A technology for output clock and signal stabilization, which is applied in the detection of the stability of the output clock signal of the phase-locked loop and the field of equipment, which can solve the problems of unstable clock signal output, achieve the effects of avoiding frequent switching, stable signal output frequency, and improving quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

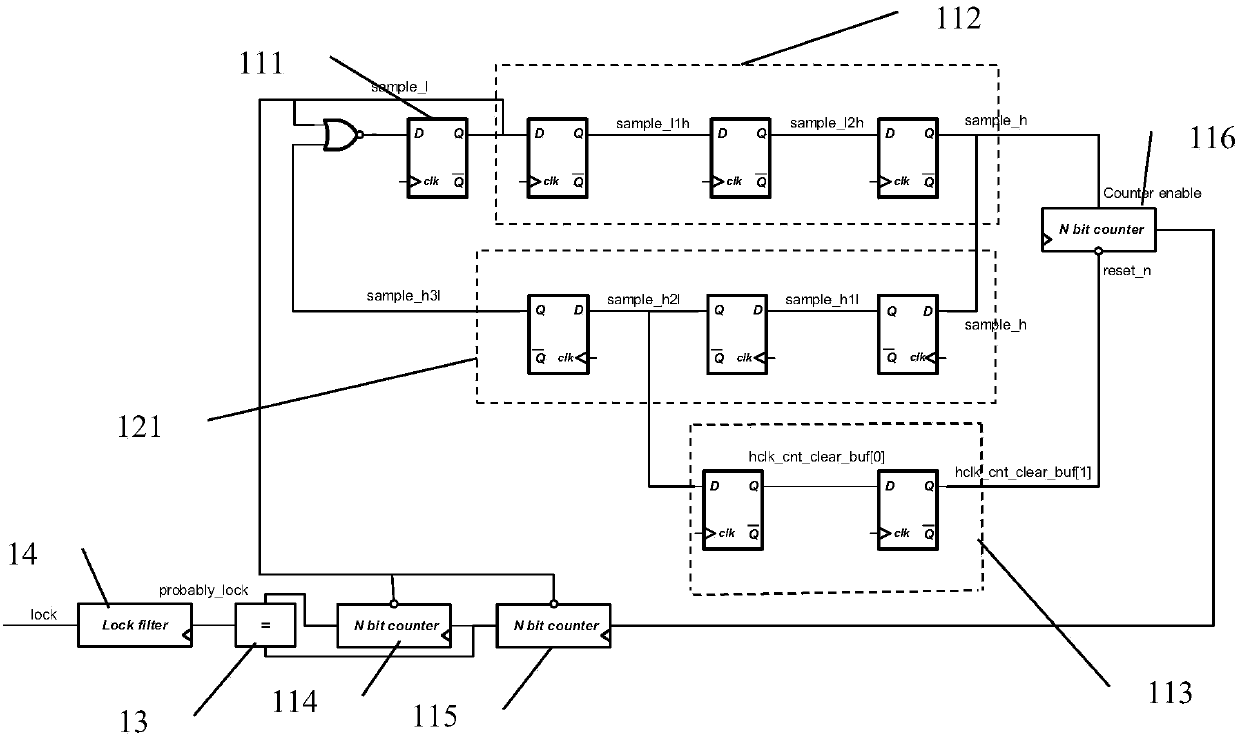

[0044] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

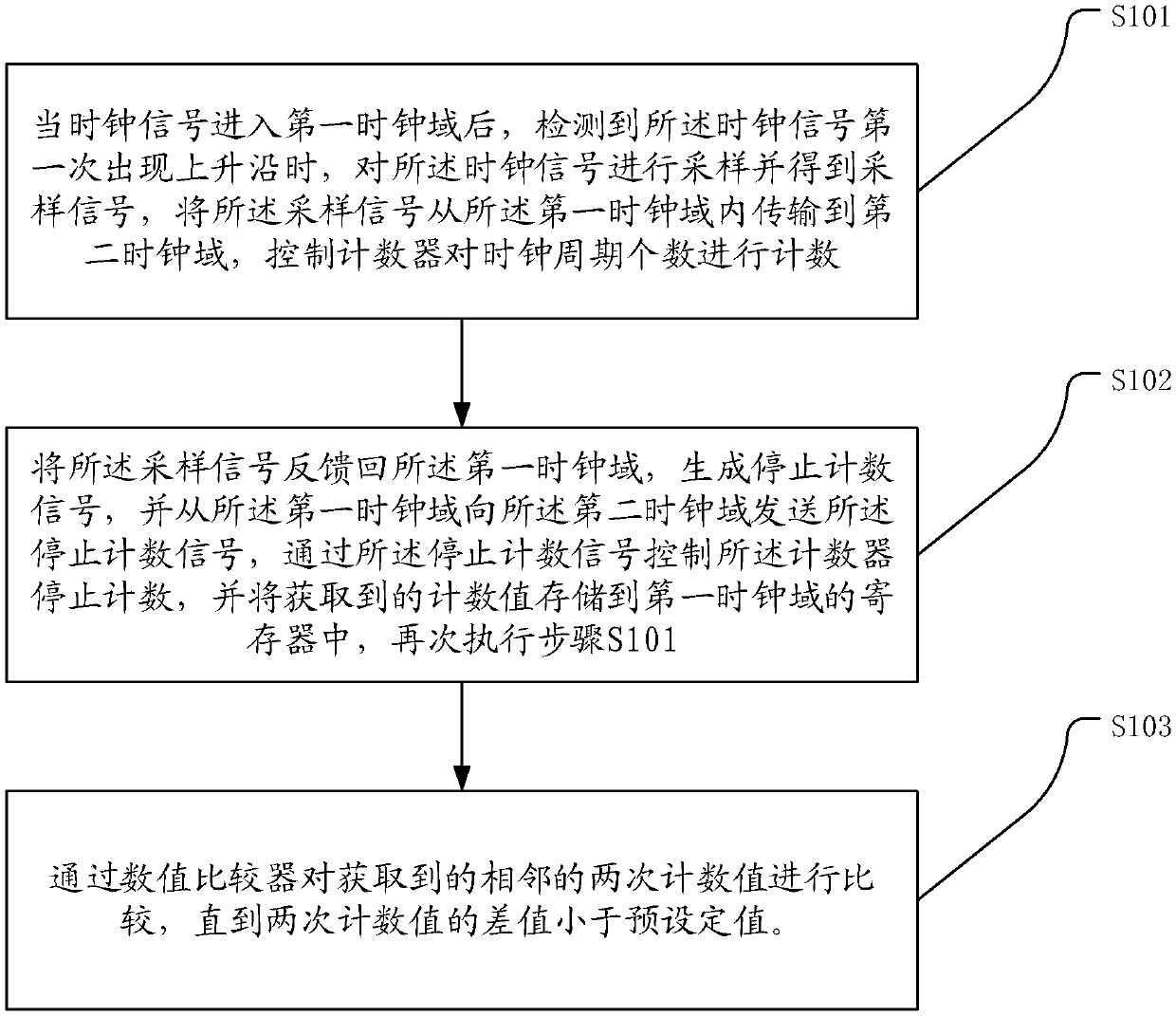

[0045] figure 1 A method for detecting the stability of a phase-locked loop output clock signal provided in Embodiment 1 of the present invention, the method includes:

[0046] S101. After the clock signal enters the first clock domain and detects that the clock signal has a rising edge for the first time, sample the clock signal to obtain a sampling signal, and transfer the sampling signal from the first clock domain transmit to the second clock domain, and control the second counter in the second clock domain to count the number of clock cycles;

[0047] S102. Feed back the sampling signal to the first clock domain, generate a stop counting signal, and send the stop counting signal from the first clock domain to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com