A 3D NAND manufacturing method

A manufacturing method and technology of substrate structure, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve problems such as peeling, device reliability and frequency reduction, wafer scrapping, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025]Hereinafter, exemplary embodiments of the present disclosure will be described in more detail with reference to the accompanying drawings. Although the drawings show exemplary embodiments of the present disclosure, it should be understood that the present disclosure can be implemented in various forms and should not be limited by the embodiments set forth herein. On the contrary, these embodiments are provided to enable a more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

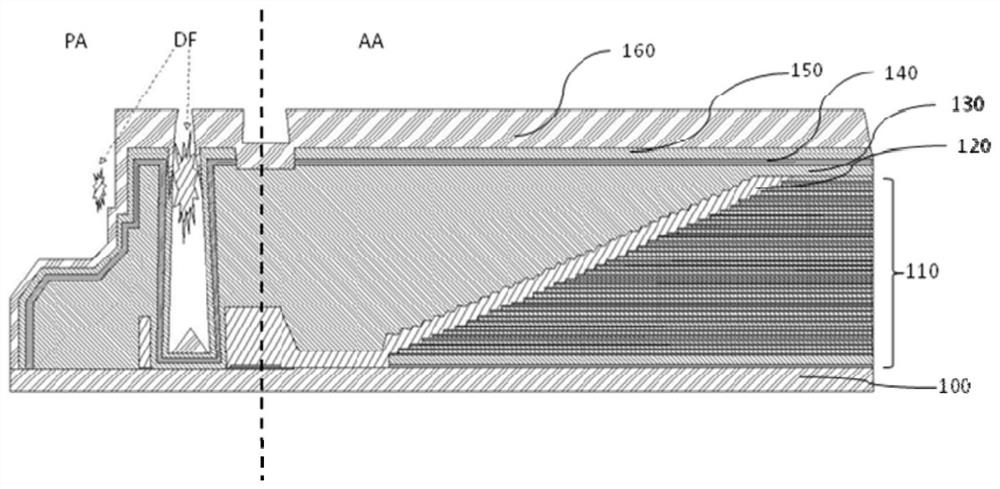

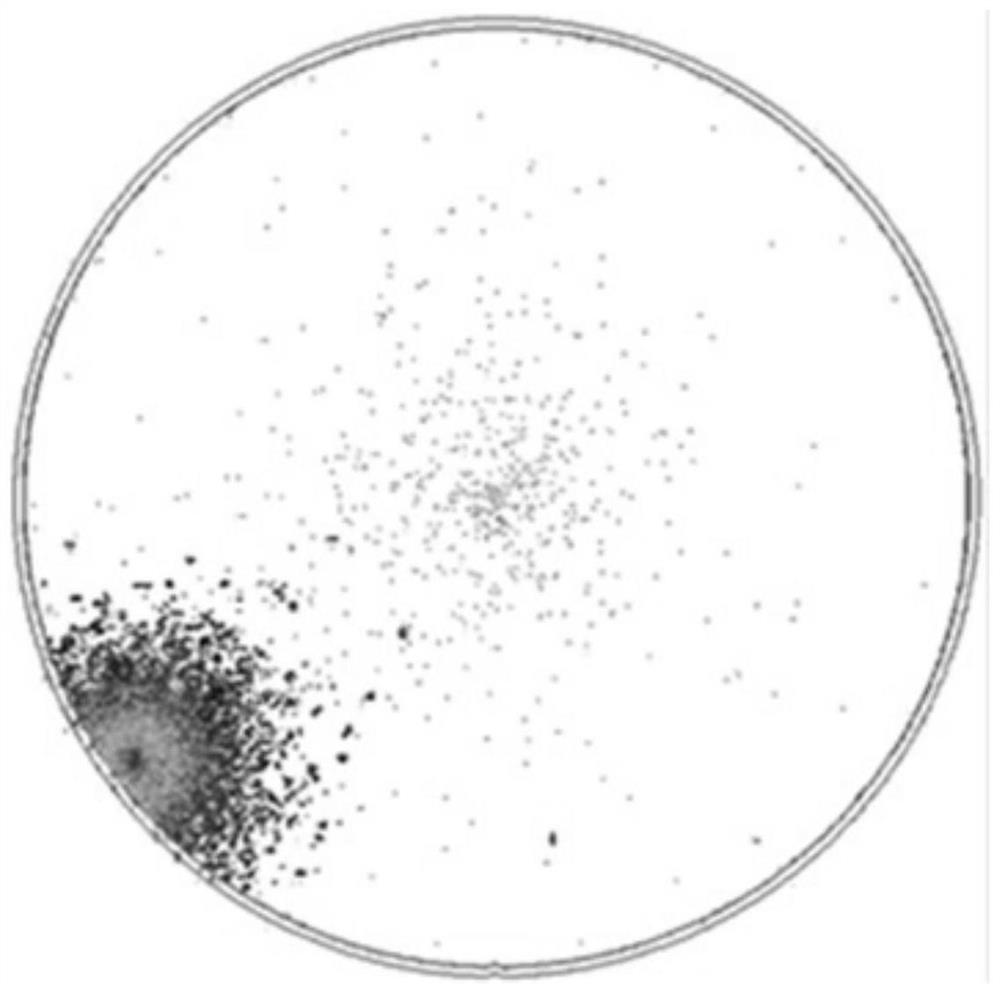

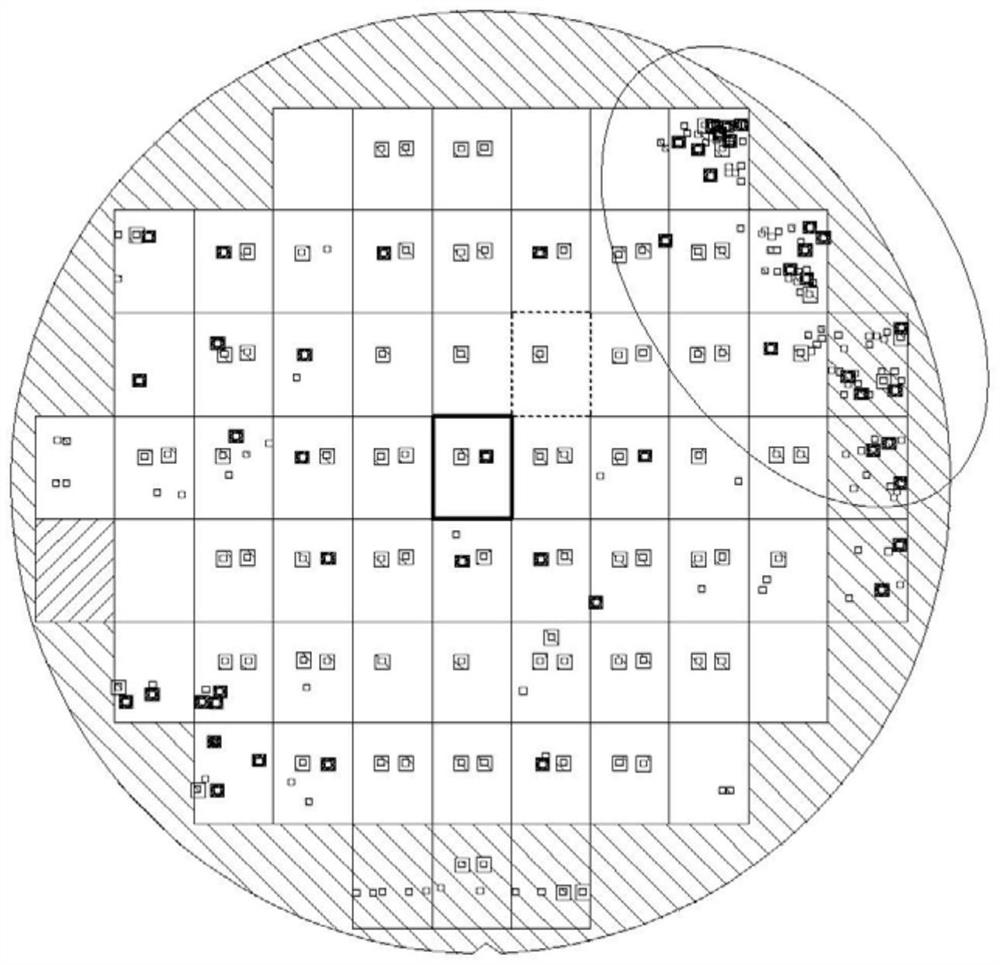

[0026]Figure 3(a)-3(g) A method of forming a 3D NAND according to an embodiment of the present invention is shown.

[0027]First, a substrate structure is provided, which has a substrate 300, a stepped structure 310 formed by an ON stack formed on the substrate 300, a high density plasma (HDP) deposition layer 320 and a TEOS layer 330 covering the stepped structure 310.

[0028]As shown in FIG. 3(a), after the steps are formed, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com