Wafer surface appearance control system and control method

A surface topography and control method technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve process defects such as wafer surface topography changes exceeding process specifications, wafer exposure, etc., and automatically adjust wet etching etc. to achieve good surface morphology and avoid defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

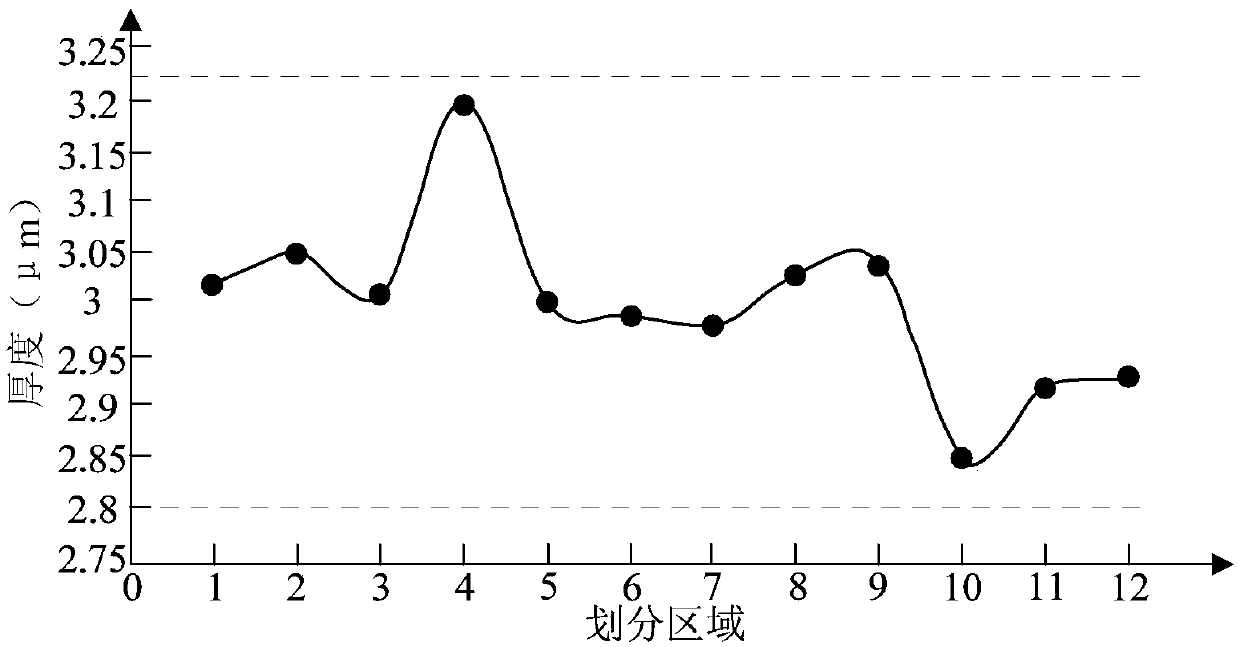

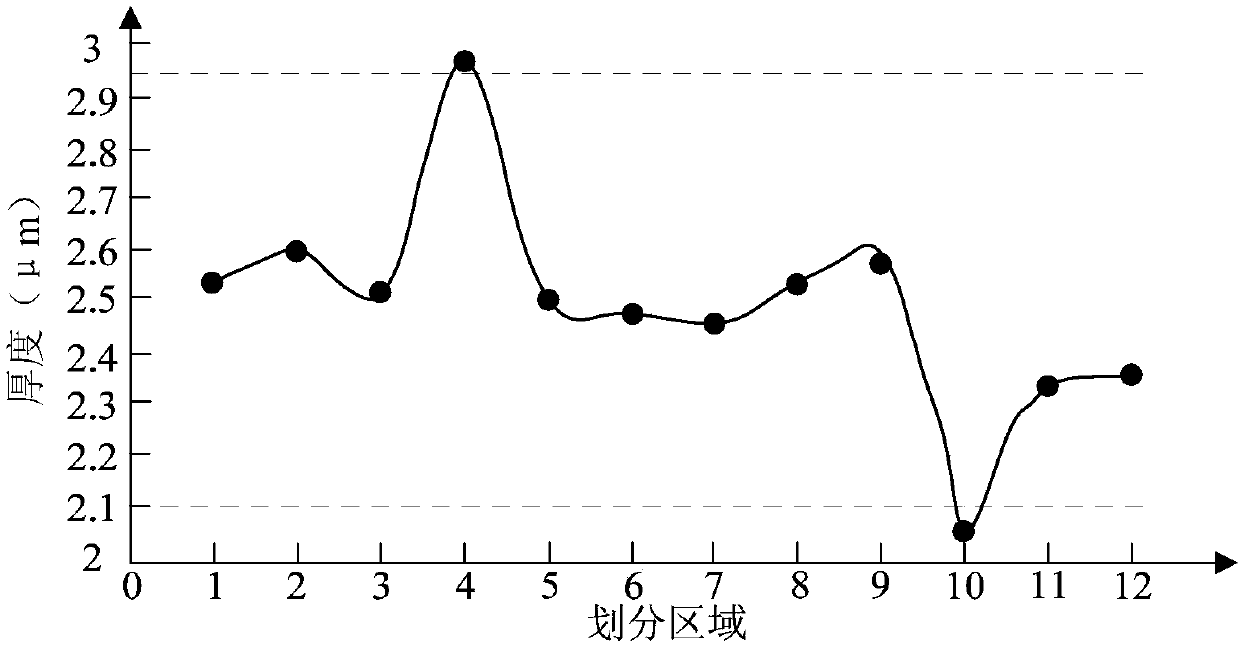

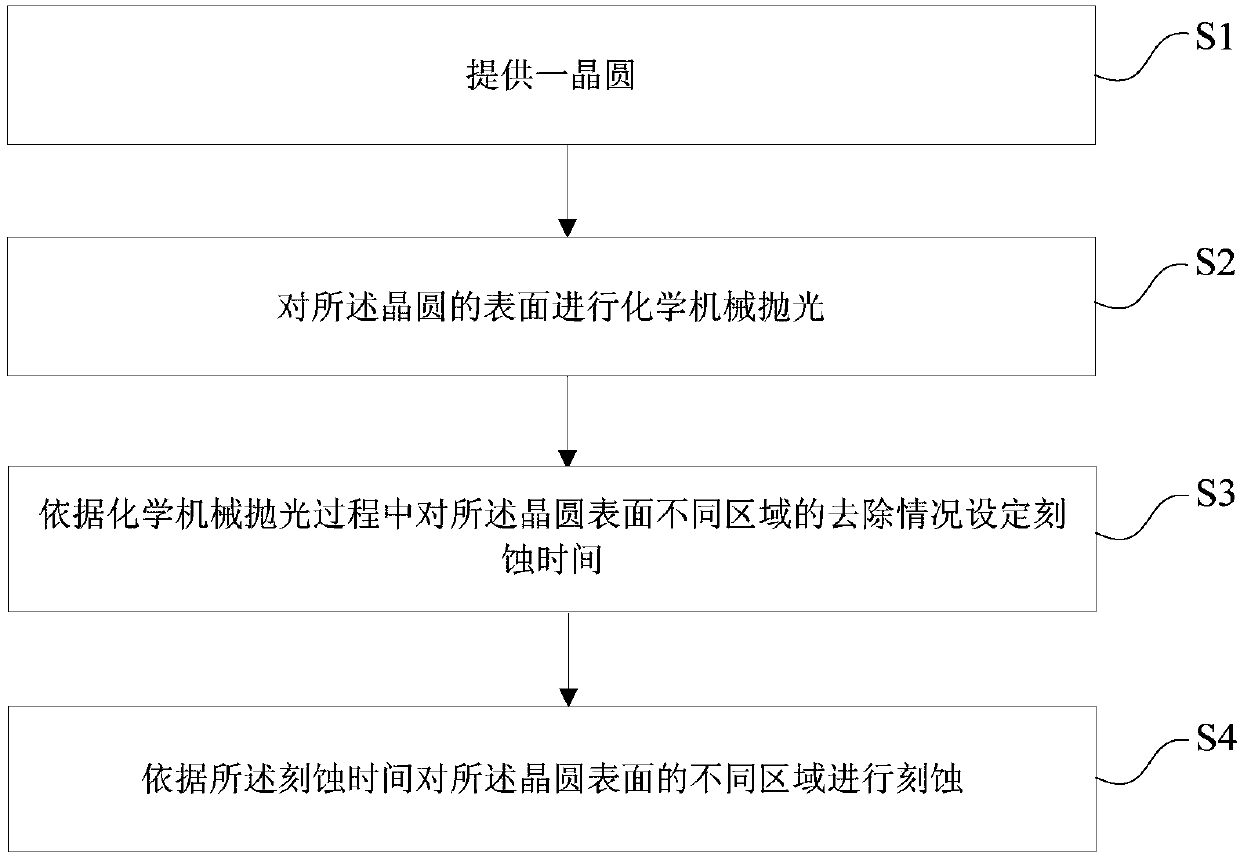

[0057] see image 3 , the present invention provides a method for controlling the surface topography of a wafer, the method for controlling the surface topography of the wafer includes the following steps:

[0058] 1) providing a wafer;

[0059] 2) Carry out chemical mechanical polishing to the surface of described wafer;

[0060] 3) setting the etching time according to the removal of different regions of the wafer surface during the chemical mechanical polishing process;

[0061] 4) Etching different regions of the wafer surface according to the etching time.

[0062] In step 1), see image 3 In step S1, a wafer is provided.

[0063] As an example, the wafer may be a silicon wafer, a sapphire wafer, or a gallium nitride wafer, etc. Preferably, in this embodiment, the wafer is a silicon wafer. A semiconductor device structure may be formed in the wafer, preferably, a back-illuminated image sensor may be formed in the wafer. Of course, in other examples, the wafer may also...

Embodiment 2

[0086] read on Figure 6 , this embodiment also provides a wafer surface topography control system, the wafer surface topography control system is used to implement the wafer surface topography control method described in Embodiment 1, the wafer surface topography The control system includes: a chemical mechanical polishing device 1, which is used to chemically mechanically polish the surface of the wafer 5; a measuring device 2, which is used to measure the chemical mechanical polishing The thickness of each region of the wafer 5; the setting module 3, the setting module 3 is connected with the measuring device 2, and is used to set the etching time according to the structure measured by the measuring device 2; An etching device 4, the etching device 4 is connected to the setting module 3, and is used to etch different regions of the surface of the chemically mechanically polished wafer 5 according to the etching time set by the setting module 3 .

[0087] As an example, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com