Data prefetching system and method applied to SOC architecture

A data prefetching and prefetching technology, applied in memory systems, electrical digital data processing, architectures with a single central processing unit, etc., can solve problems such as reducing operating efficiency, achieve low power consumption, efficient mapping relationships, and flexible methods Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be described in further detail below in conjunction with the examples and the accompanying drawings, but the embodiments of the present invention are not limited thereto.

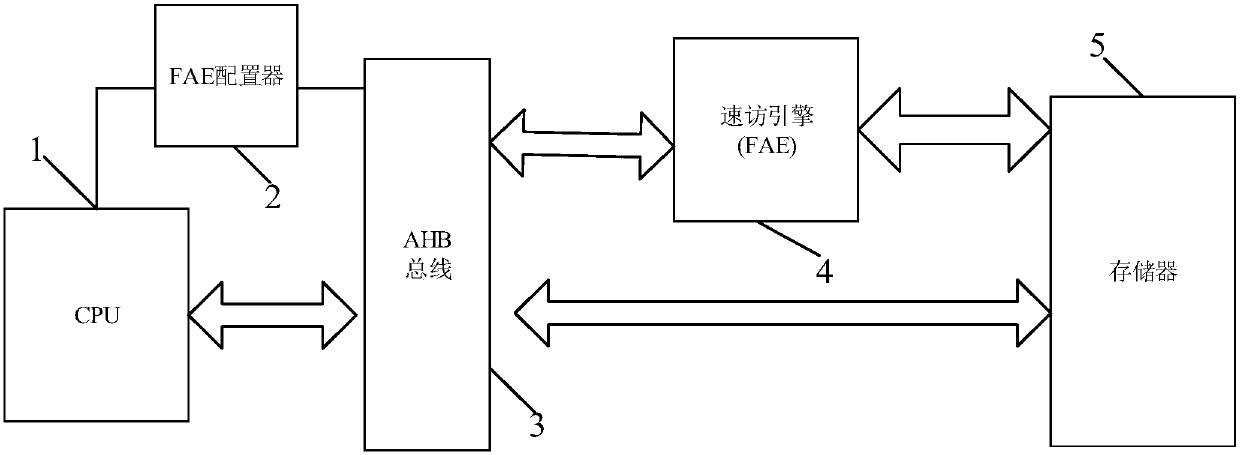

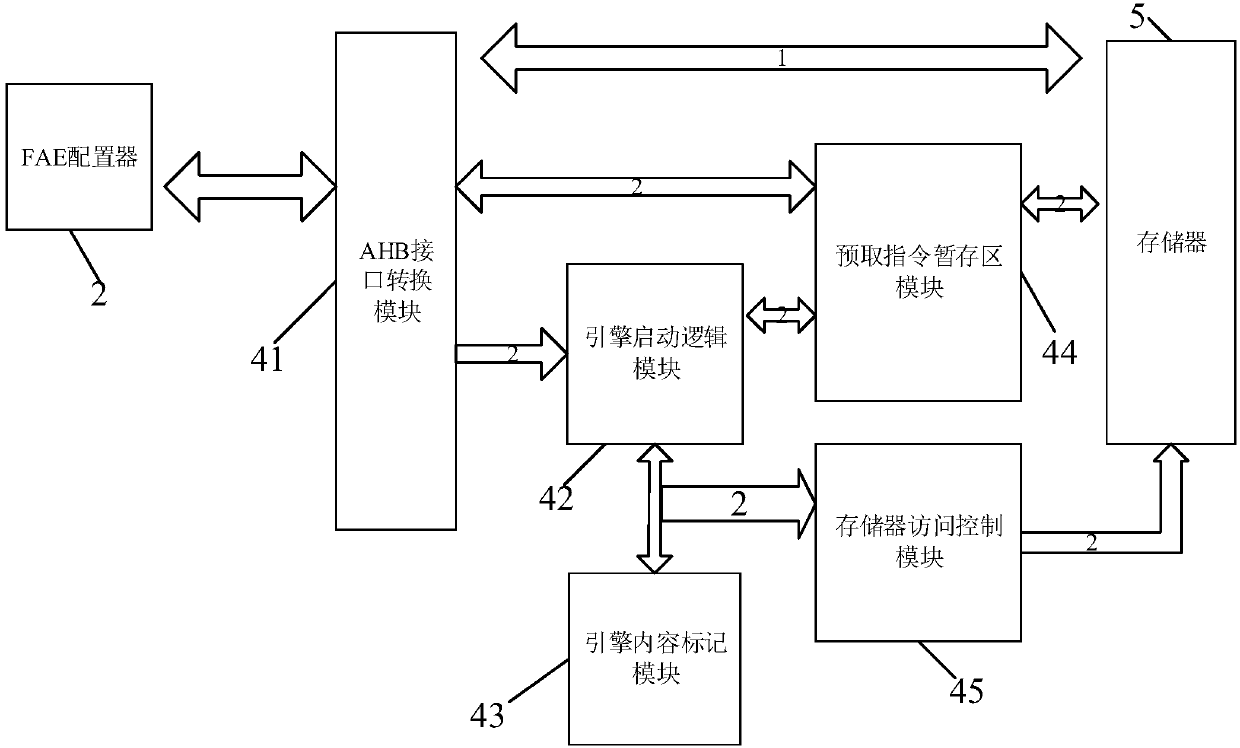

[0041] In order to solve the technical defect that the CPU reads the external memory at a slow speed in the prior art, the present invention provides a SOC architecture configured with a fast access engine and a method for accessing the memory. The present invention optimizes and improves on the basis of the existing SOC architecture, and mainly realizes fast reading of memory data by adding a fast access engine between the CPU and the memory. In addition, the improved SOC architecture provides a memory access method, so as to realize fast reading of memory data. The technical solution of the present invention will be specifically described in conjunction with the following embodiments.

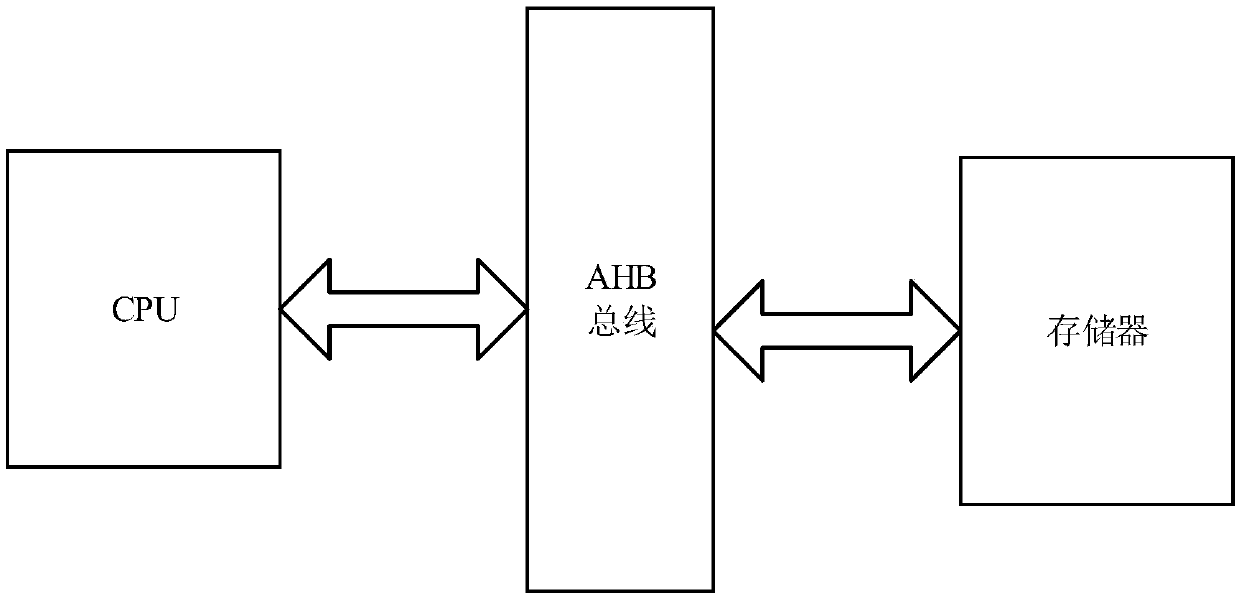

[0042] See first figure 1 , which is a schematic diagram of the SOC architecture of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com