I2C (Inter-Integrated Circuit) host adapter system

A host adapter and server technology, applied in the direction of detecting faulty computer hardware, etc., can solve the problems of cumbersome waste of time, not so easy to use, waste of time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

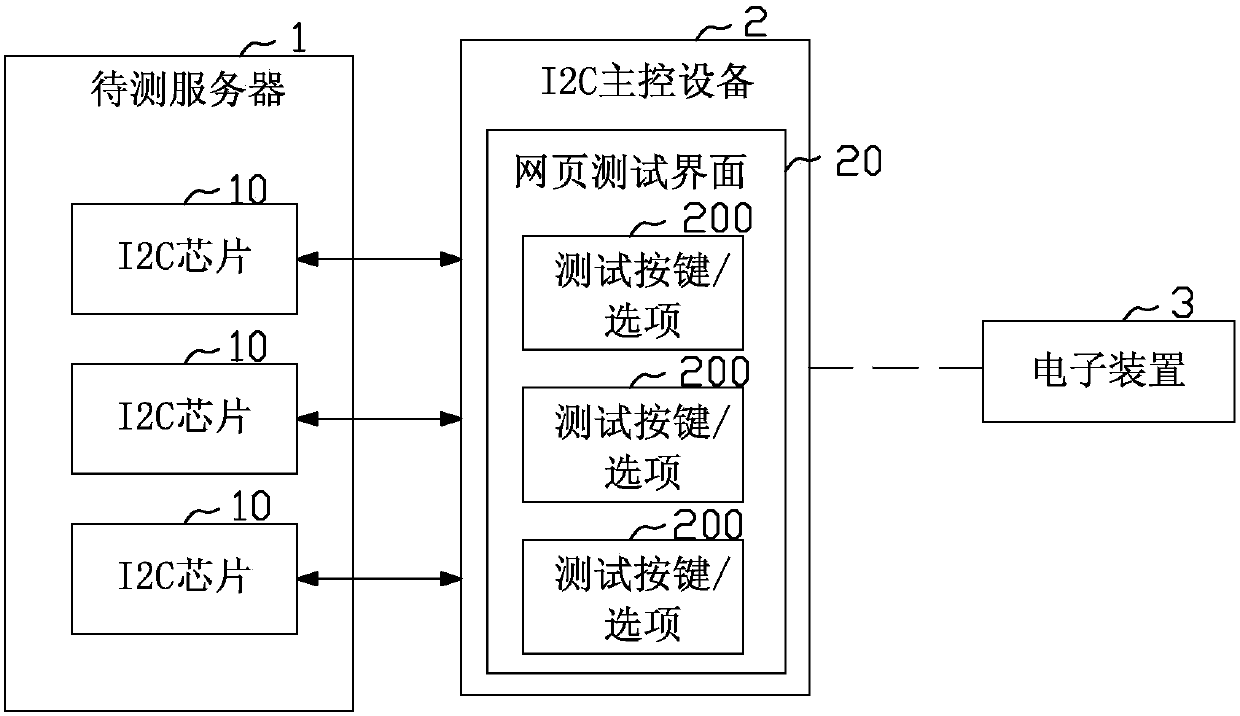

[0017] see figure 1 As shown, the present invention provides an I2C host adapter system, which includes: a server to be tested 1 , the I2C master control device 2 and an electronic device 3 .

[0018] The server 1 to be tested has at least one I2C chip 10, three of which are taken as an example in this embodiment.

[0019] The I2C master control device 2, which is electrically connected to a plurality of I2C chips 10 of the server to be tested 1, provides a webpage test interface 20 corresponding to the I2C chip 10, and the network test interface 20 includes at least one test button / option 200. In this embodiment, the I2C master device 2 is electrically connected to the I2C chip 10 through an I2C bus.

[0020] The electronic device 3 is connected to the I2C main control device 2 through the network, and the user controls the I2C main control device 2 to send a test command through the electronic device 3 and through the web page test interface 20. In this embodiment, After ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com