Stream reference register with double vector and dual single vector operating modes

A technology of registers and data registers, applied in memory systems, instruments, machine execution devices, etc., can solve problems such as difficult address generation and access resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

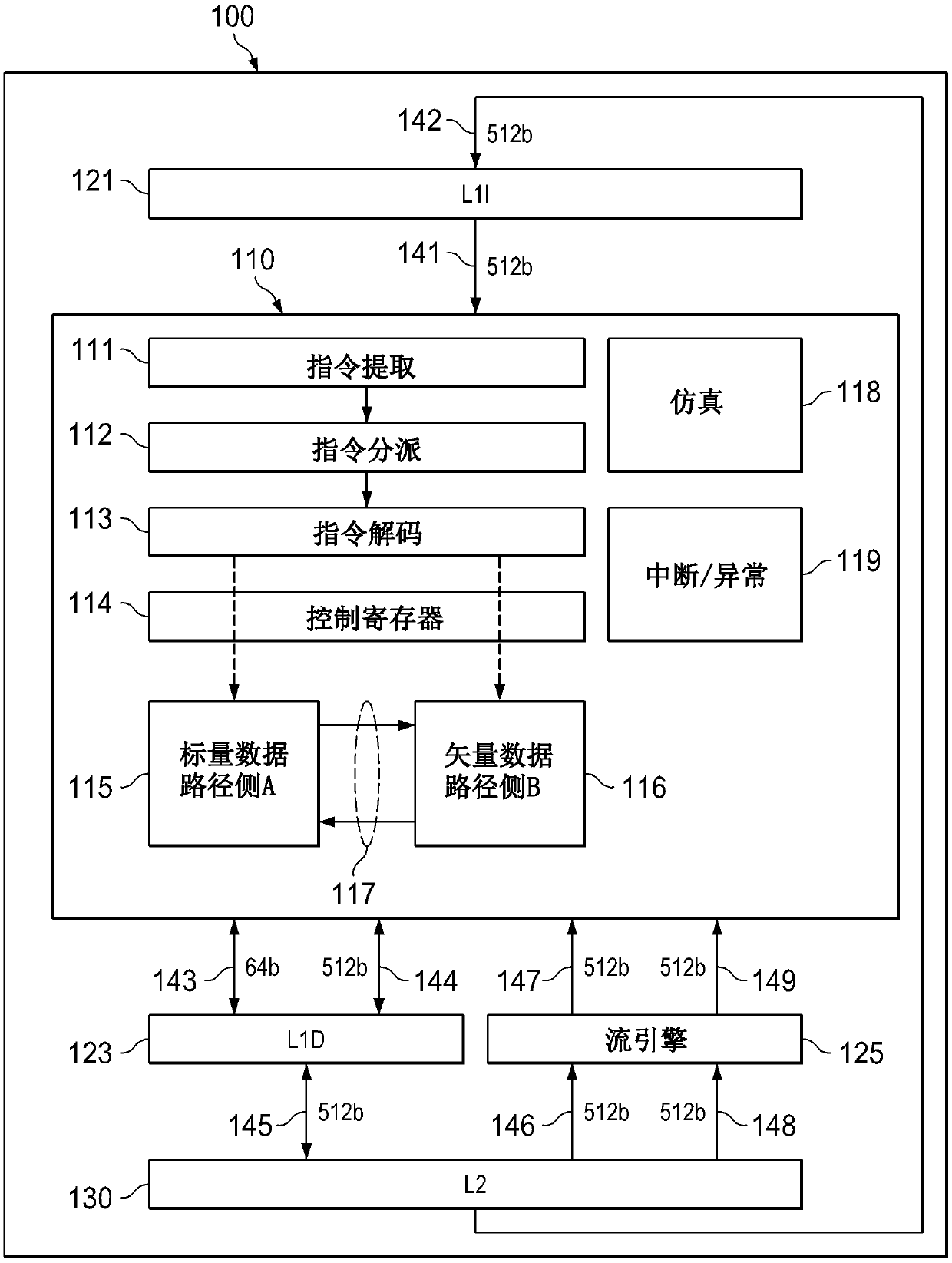

[0044] figure 1 A dual scalar / vector datapath processor in accordance with a preferred embodiment of the present invention is described. The processor 100 includes separate L1 instruction register (L1I) 121 and L1 data register (L1D) 123 . Processor 100 includes a combined level two instruction / data cache (L2) 130, which holds both instructions and data. figure 1 The connection (bus 142 ) between the L1 instruction register 121 and the L2 combined instruction / data register 130 is illustrated. figure 1 The connection between the L1 data cache 123 and the L2 combined instruction / data cache 130 (bus 145) is illustrated. In a preferred embodiment of the processor 100 , the L2 combined I / D cache 130 stores both instructions to back up the L1 Irreg 121 and stores data to back up the L1 data cache 123 . In a preferred embodiment, the two-level combined instruction / data cache 130 is further implemented with known but figure 1 connection to higher-level cache and / or main memory in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com