Shift register, gate drive circuit and display device

A technology for shift registers and gates, which is applied in the field of gate drive circuits, display devices, and shift registers, and can solve problems such as unfavorable conditions, single drive mode of gate drive circuits, and reduced energy consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

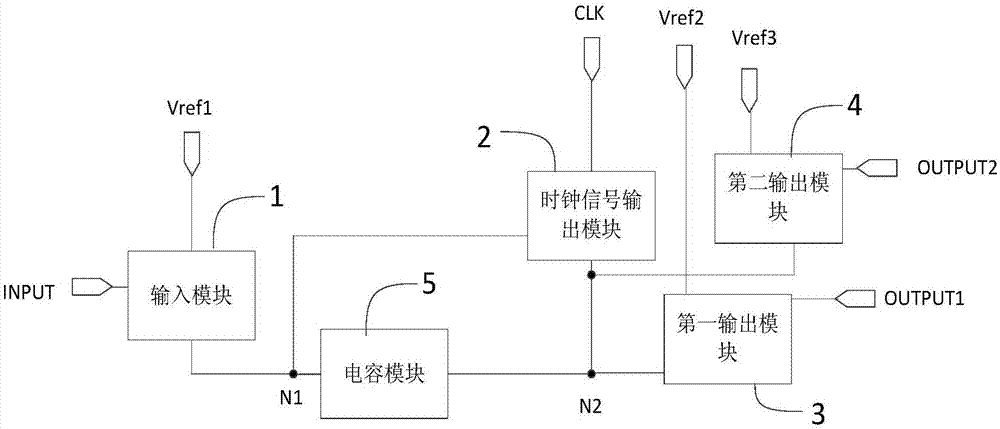

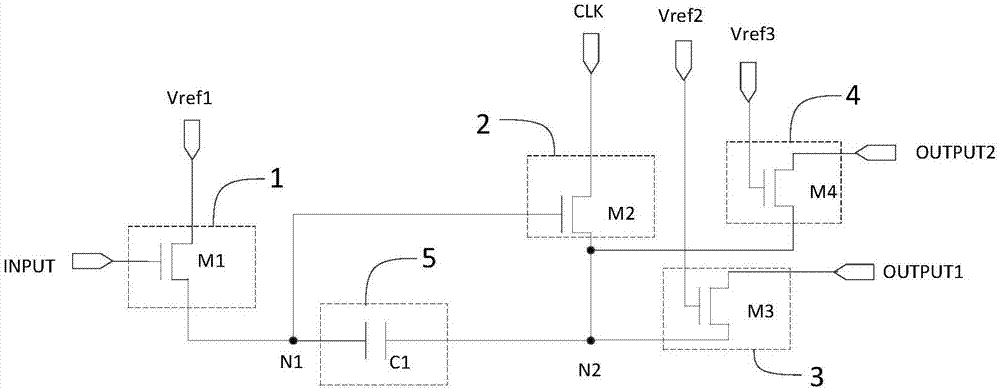

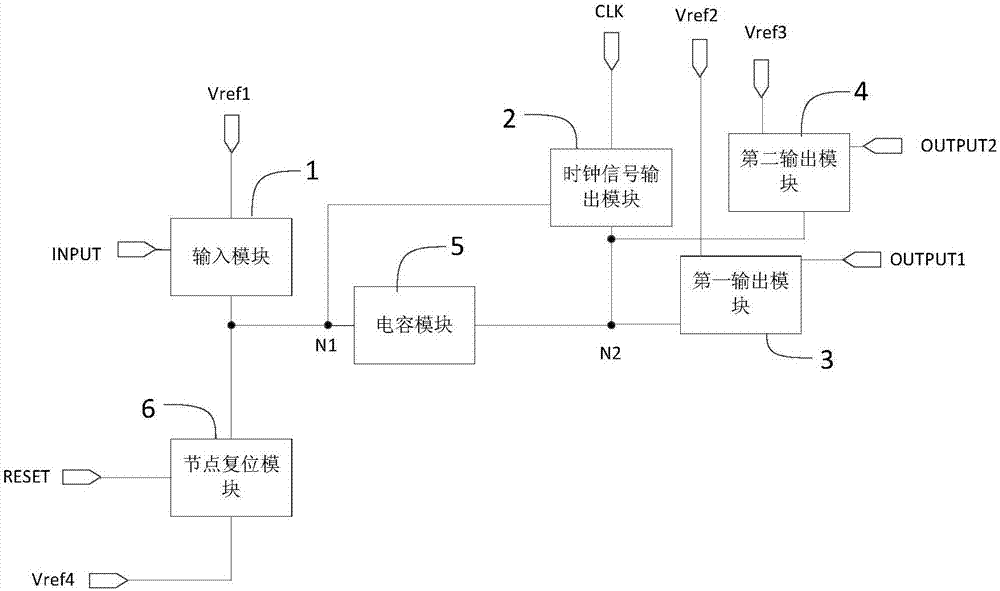

[0099] by figure 1 The circuit configuration shown and Figure 5 The timing diagram shown is illustrated:

[0100] T1 stage, INPUT=1, CLK=0, Vref2=0, Vref3=1.

[0101] Since INPUT=1, the first switch transistor is turned on, and the first reference signal sent by the first reference signal segment is provided to the first node through the turned-on first switch transistor, so that the first node maintains a high potential.

[0102] In T2 stage, INPUT=0, CLK=1, Vref2=1, Vref3=0.

[0103] Due to the effect of the first capacitor, the potential of the first node remains at a high potential, the second switch transistor is turned on, and the clock signal sent by the clock signal terminal is provided to the second node through the turned-on second switch transistor, because the second reference signal at this time The second reference signal sent by the terminal is a high potential, the third switch transistor is turned on, and the potential of the second node is provided to the...

Embodiment 2

[0105] by figure 1 The circuit configuration shown and Figure 6 The timing diagram shown is illustrated:

[0106] In T1 stage, INPUT=1, CLK=0, Vref2=1, Vref3=0.

[0107] Since INPUT=1, the first switch transistor is turned on, and the first reference signal sent by the first reference signal segment is provided to the first node through the turned-on first switch transistor, so that the first node maintains a high potential.

[0108] In T2 stage, INPUT=0, CLK=1, Vref2=0, Vref3=1.

[0109] Due to the effect of the first capacitor, the potential of the first node remains at a high potential, the second switch transistor is turned on, and the clock signal sent by the clock signal terminal is provided to the second node through the turned-on second switch transistor, because the third reference signal at this time The third reference signal sent by the terminal is a high potential, the fourth switch transistor is turned on, and the potential of the second node is provided to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com