Wafer Planarization Method

A flattening method and wafer technology, applied in the manufacture of electrical components, circuits, semiconductor/solid-state devices, etc., can solve the problem that cerium oxide abrasive particles are easy to remain on the surface of silicon wafers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] A specific implementation of a wafer planarization method provided by the present invention will be described in more detail below with reference to schematic diagrams. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

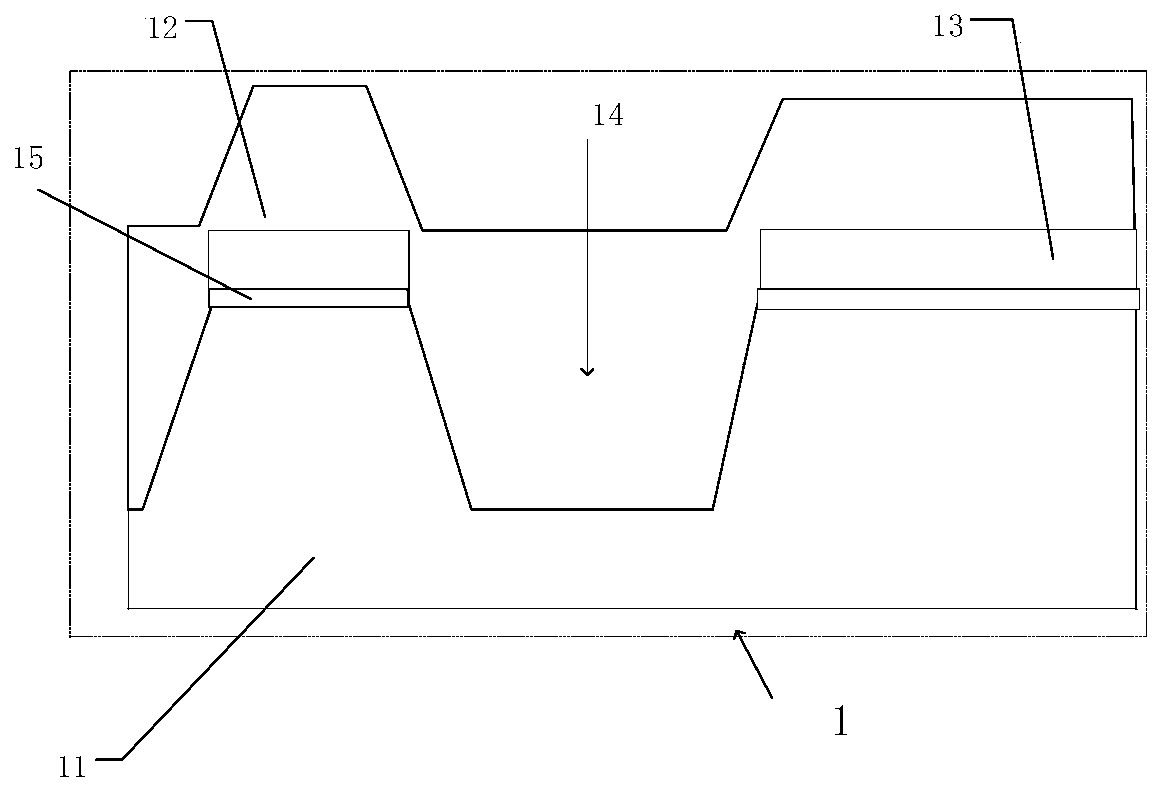

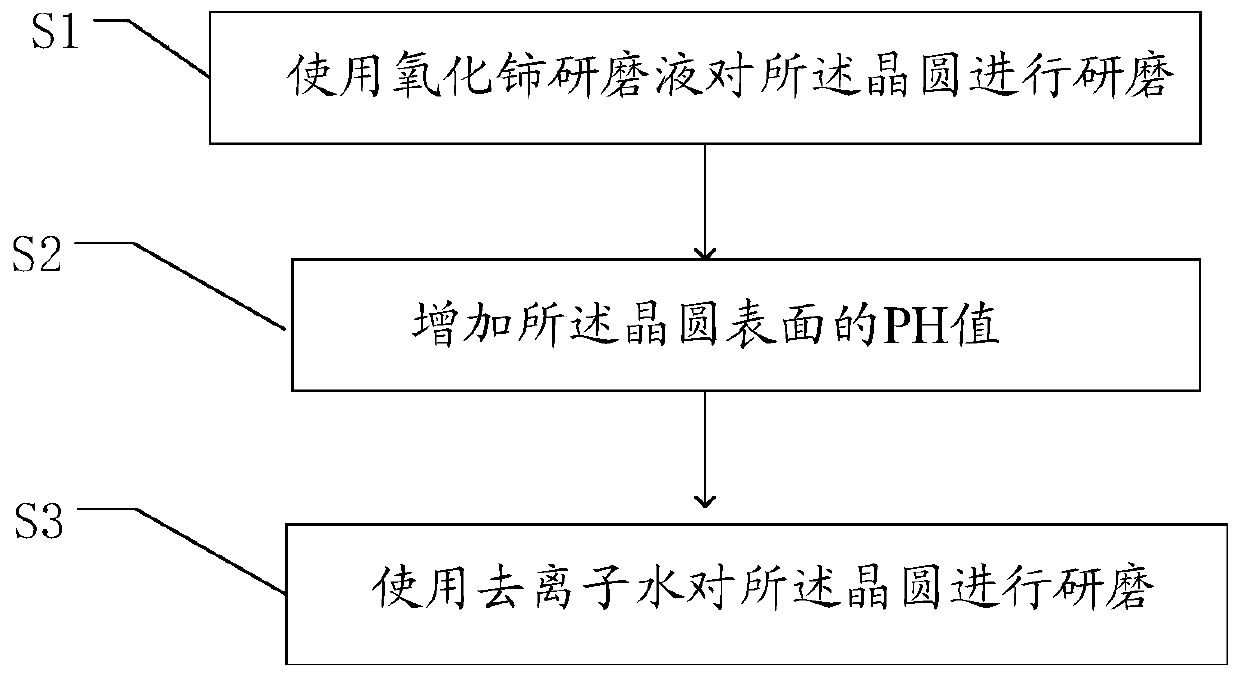

[0025] refer to Figure 1-Figure 2 , which is a schematic diagram of the wafer structure provided by the present invention and a wafer planarization method, the wafer 1 includes a substrate 11 and an oxide layer 12; a trench 14 is formed in the substrate 11, and the oxide layer 12 covering the substrate 11 and filling the trench 14, grinding the wafer 1 on a polishing pad to planarize the wafer 1, the method for planarizing the wafer 1 includes, S1: using Grinding the wafer 1 wit...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com