Power semiconductor chip, sub-module comprising the chip and crimping-type packaging module

A technology for power semiconductors and packaging modules, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, and semiconductor/solid-state device components, etc. The effect of improving pressure stability, improving yield and simplifying production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

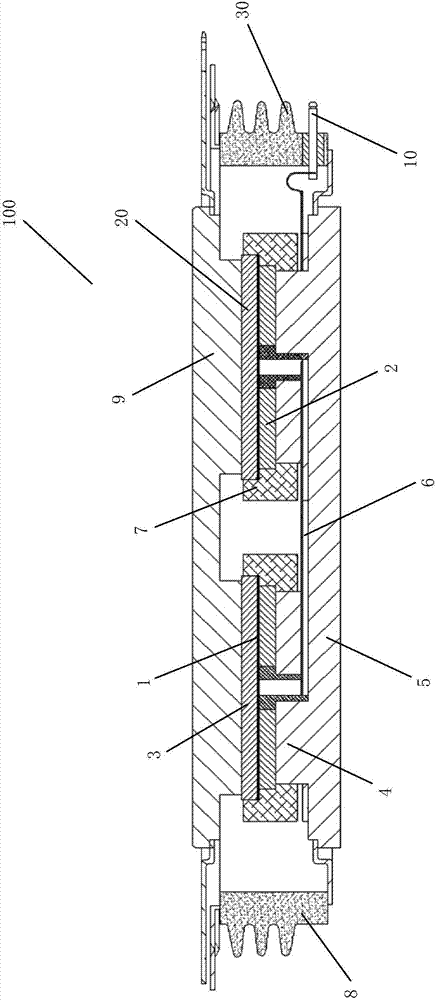

[0074] as attached figure 1 As shown, a specific embodiment of a crimping package module, the module 100 further includes:

[0075] Shell 30, the shell 30 comprises the shell 8 of ceramic material, the cap 9 as the first electrode, and the base 5 as the second electrode, the cap 9 is fixed on the top of the shell 8, the base 5 is fixed on the bottom of the shell 8 At the bottom, a grid terminal 10 as a third electrode is also provided on the shell 8;

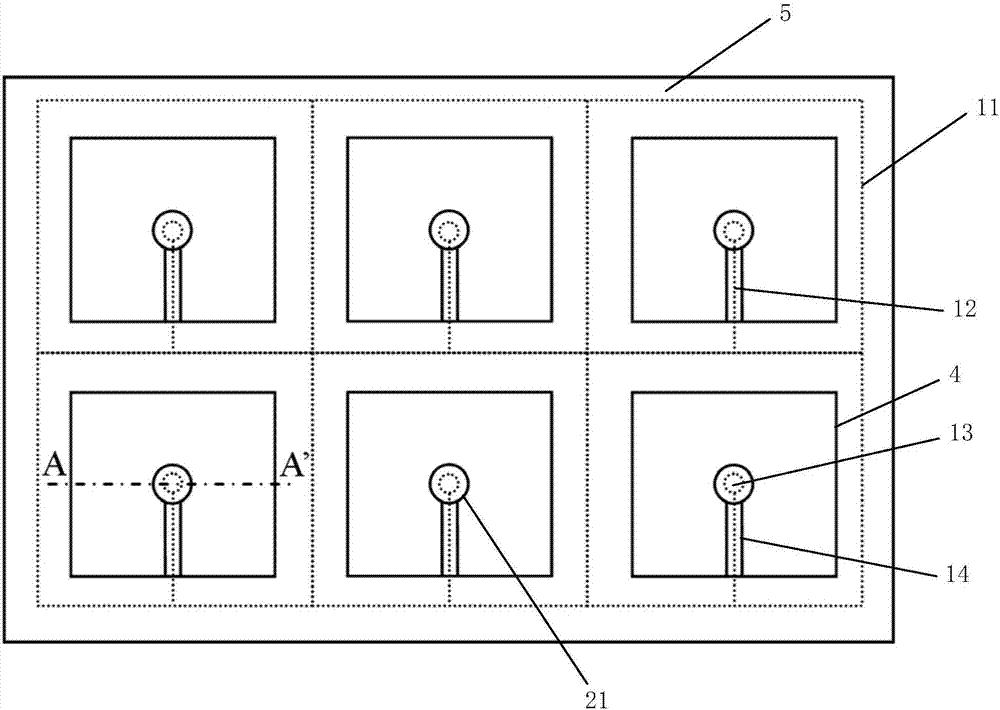

[0076] More than two sub-modules 20 arranged in the housing 30, the sub-modules 20 realize parallel crimping through the tube cover 9 and the base 5; The grid electrodes are interconnected; one side of the sub-module 20 is connected to the tube cover 9, a part of the other side of the sub-module 20 is connected to the base 5, and the other part is connected to the PCB board 6, and is connected to the grid lead-out terminal 10 after being interconnected through the PCB. .

[0077] Wherein, the first electrode serves as the col...

Embodiment 2

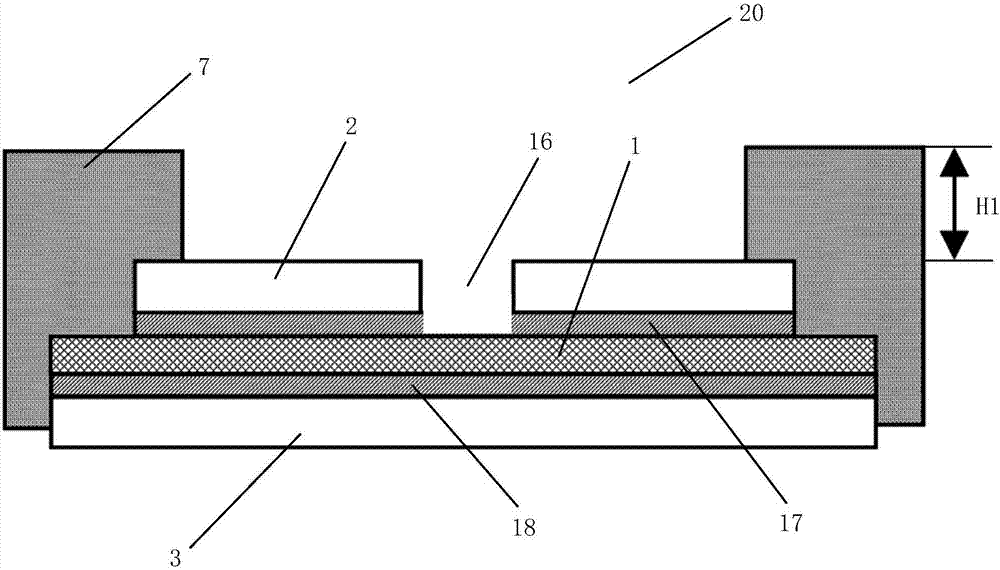

[0080] as attached figure 2 As shown, a specific embodiment of a sub-module 20 is shown. On the basis of Embodiment 1, the sub-module 20 further includes: an upper molybdenum sheet 2 , a lower molybdenum sheet 3 , and a chip 1 . The upper molybdenum sheet 2 is arranged on the upper surface of the chip 1 (between the chip 1 and the base 5 ), and the upper molybdenum sheet 2 is connected with the chip 1 through the upper sintering layer 17 . The lower molybdenum sheet 3 is arranged on the lower surface of the chip 1 (between the chip 1 and the cap 9 ), and the lower molybdenum sheet 3 is connected with the chip 1 through the lower sintering layer 18 . A through hole 16 for leading out the gate electrode 105 is provided at the center of the upper molybdenum sheet 2 . The upper molybdenum sheet 2 and the lower molybdenum sheet 3 are respectively connected to the upper and lower surfaces of the chip 1 through a silver sintered layer. The size of the molybdenum sheet is the same a...

Embodiment 3

[0085] as attached Figure 6 As shown, another specific embodiment of the sub-module 20 , on the basis of the first embodiment, the sub-module 20 further includes: an upper molybdenum sheet 2 , a lower molybdenum sheet 3 , and a chip 1 . The upper molybdenum sheet 2 is arranged on the upper surface of the chip 1 (between the chip 1 and the base 5 ), and the upper molybdenum sheet 2 is connected with the chip 1 through the upper sintering layer 17 . The lower molybdenum sheet 3 is arranged on the lower surface of the chip 1 (between the chip 1 and the cap 9 ), and the lower molybdenum sheet 3 is connected with the chip 1 through the lower sintering layer 18 . The periphery of the sub-module 20 is also provided with an insulating protective ring 7, the insulating protective ring 7 covers the terminal area 102 of the chip 1, the lower surface of the insulating protective ring 7 is higher than the lower surface of the lower molybdenum sheet 3, and the upper surface of the insulati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com