Transistor modeling method based on narrow-pulse small signal measurement

A modeling method, transistor technology, applied in neural learning methods, biological neural network models, special data processing applications, etc., can solve the problem that the small signal equivalent circuit cannot accurately describe the device, the difficulty increases, and the accuracy of the modeling result cannot be guaranteed And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with embodiment.

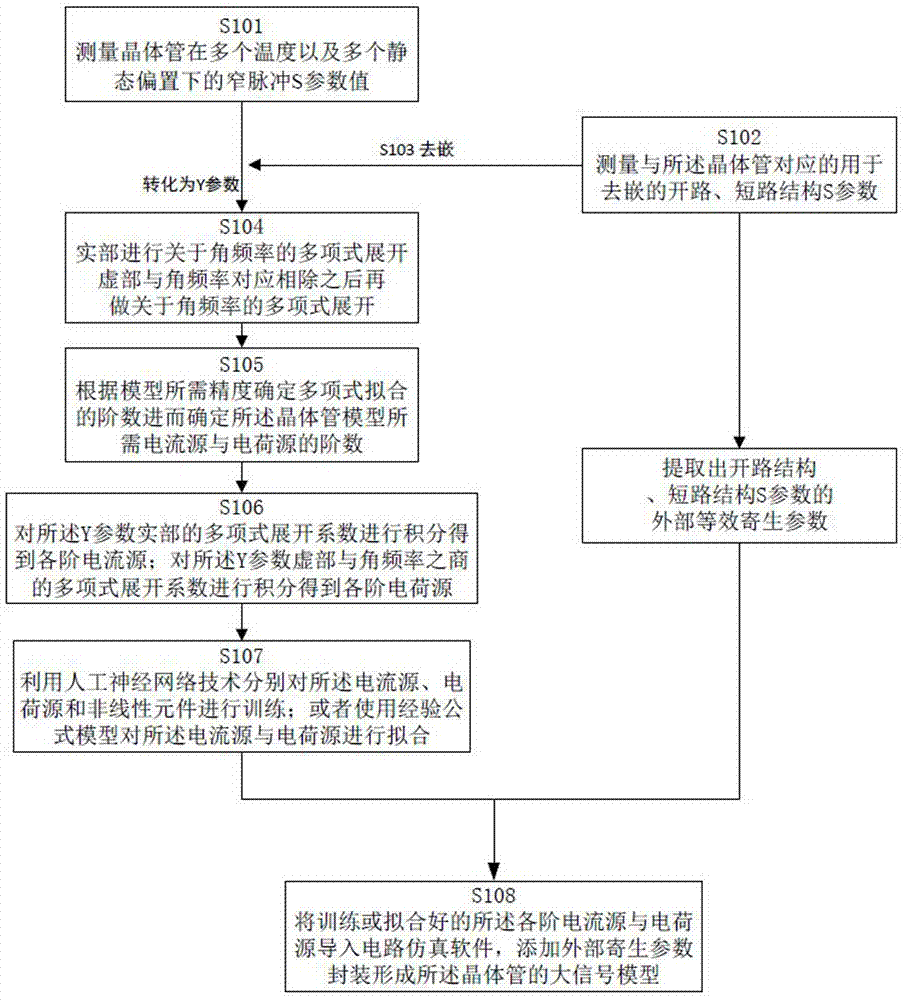

[0031] Such as figure 1 A transistor modeling method based on narrow-pulse small-signal measurements is shown, including the following steps:

[0032] S101 measures the narrow pulse S-parameters of the transistor at multiple temperatures and multiple static biases;

[0033] S102 Measure the S-parameters of the open-circuit structure and the short-circuit structure corresponding to the transistor for de-embedding, and at the same time, extract the external equivalent parasitic parameters of the S-parameters of the open-circuit structure and the short-circuit structure;

[0034] S103 uses the S parameters of the open circuit structure and the short circuit structure to de-embed the narrow pulse S parameters. The specific method is: convert the measured narrow pulse S parameters into Y parameters, and convert the S parameters of the open circuit structure into Y parameters. Convert th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com