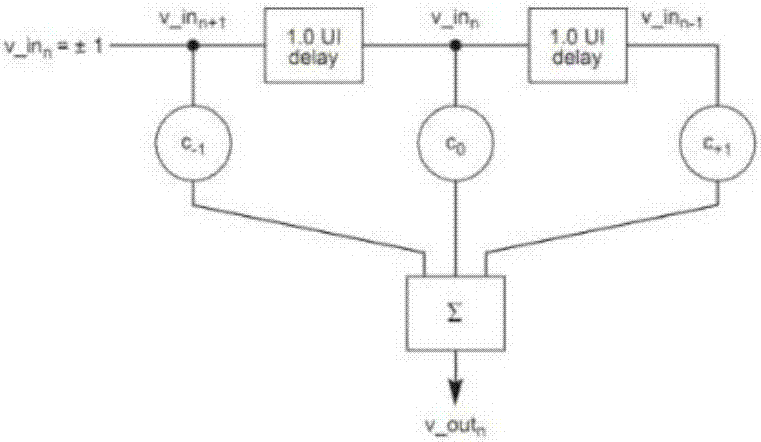

CScripts-based method for adjusting PCIe Tx Eq at CPU end of Purley platform

A platform and pre-adjustment technology, applied in program control design, instruments, electrical and digital data processing, etc., can solve the problems of occupying test engineers, low inspection efficiency, and long time, and achieve the effect of improving test efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

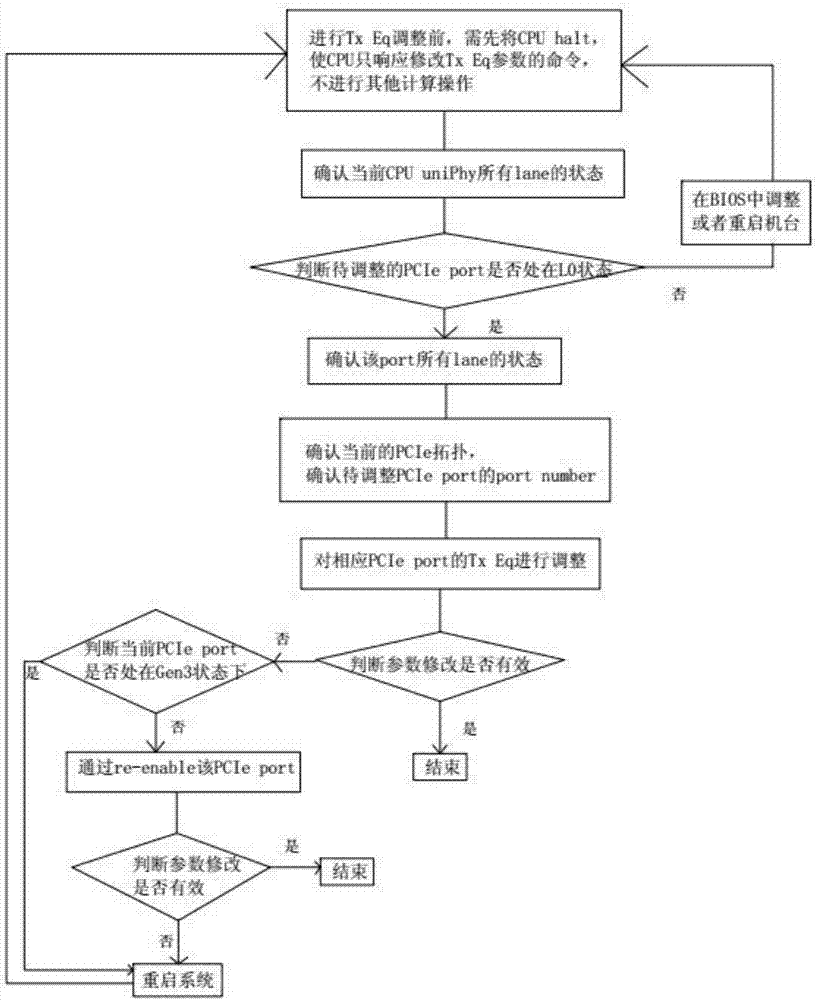

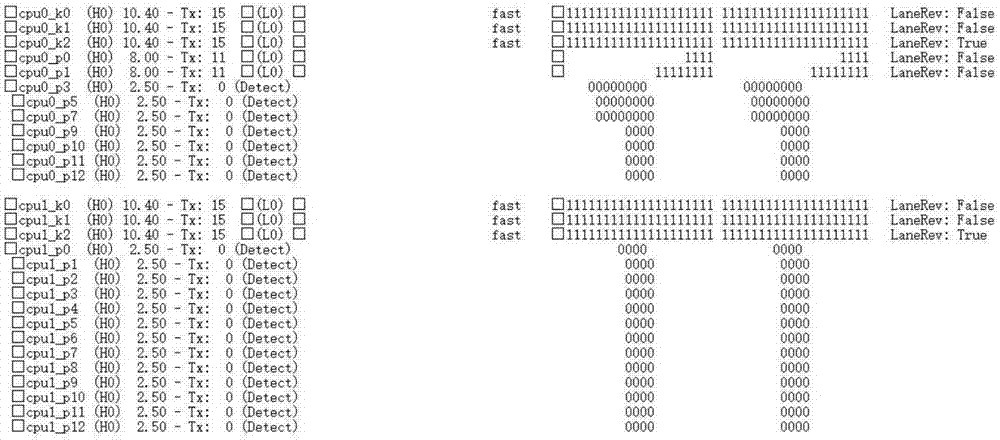

[0026] Such as figure 2 As shown, a method for adjusting the PCIe Tx Eq on the CPU side of the Purley platform based on CScripts includes the following steps: S1. Before adjusting the Tx Eq, the CPU needs to be halted first, so that the CPU only responds to commands that modify the Tx Eq parameters, and does not perform Other computing operations; S2. Confirm the status of all lanes of the current CPU uniPhy, such as image 3 As shown, determine whether the PCIe port to be adjusted is in the L0 state, yes, confirm the status of all lanes of the port; no, adjust or restart the machine in the BIOS; S3, confirm the current PCIe topology, and confirm the status of the PCIe port to be adjusted port number; S4. Adjust the Tx Eq of the corresponding PCIe port; S5. Determine whether the parameter modification is valid. If the modification is invalid, determine whether the current PCIe port is in the Gen3 state. If the current PCIe port is in the Gen3 state, restart Execute from step...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com