A Wiring Method of Adder Supporting Pin Swapping

A wiring method and adder technology, applied in the direction of logic circuits using specific components, can solve the problems of reducing the success rate of wiring and increasing the complexity of wiring, so as to improve the bypassability, improve chip utilization, and save logic resources. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

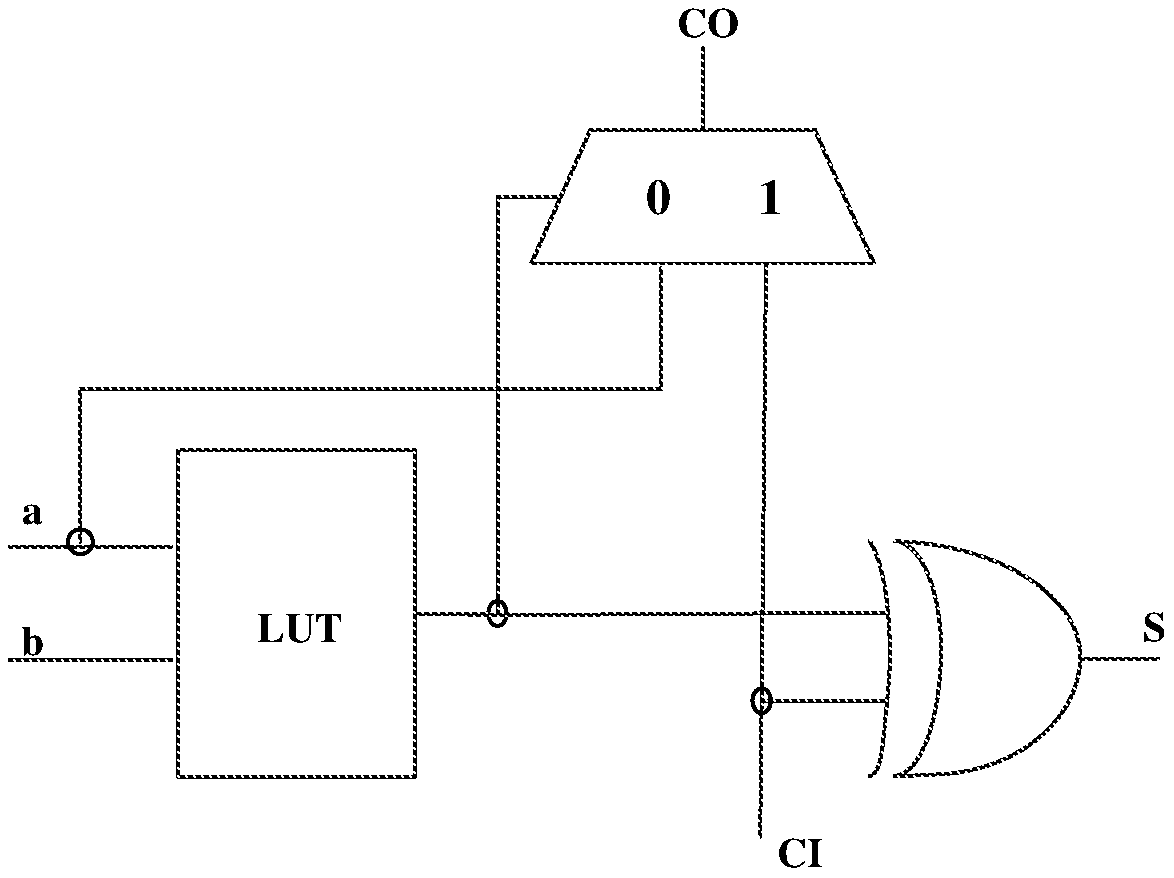

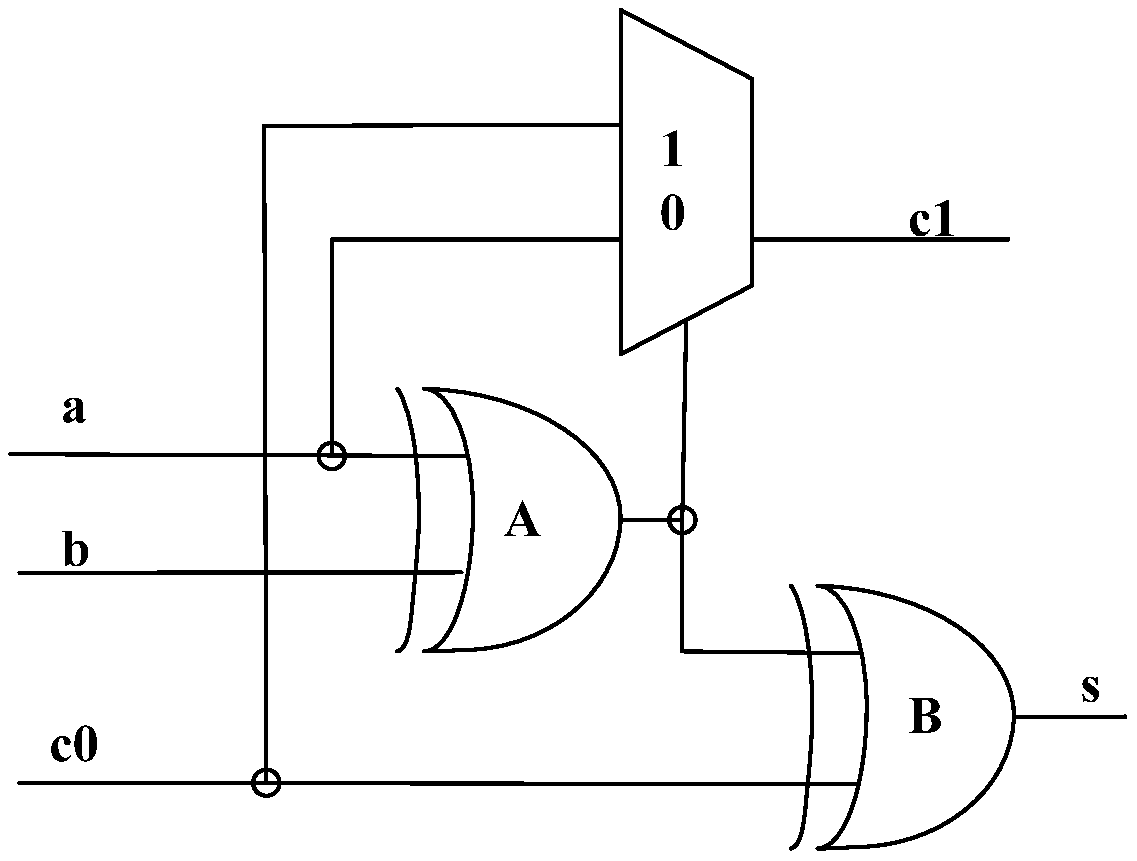

[0022] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

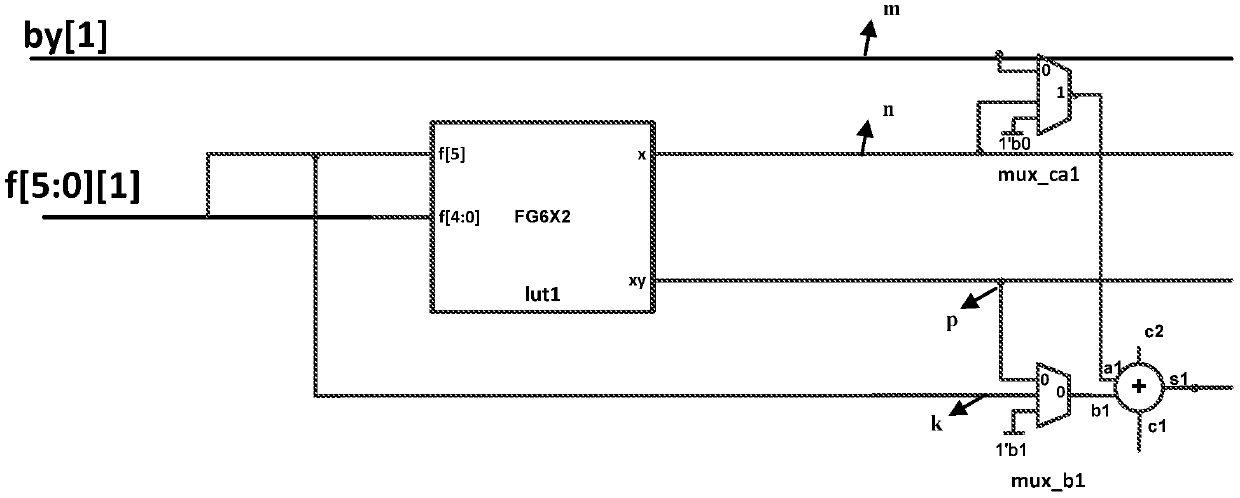

[0023] The methods in the following embodiments of the present invention are implemented based on the first chip C1 of the cloud series in the FPGA chip. figure 2 A schematic structural diagram of a programmable logic module in a C1 architecture provided by an embodiment of the present invention. C1 is the first chip of the cloud series in the FPGA chip, mainly used in the field of high-speed communication. Such as figure 2 As shown, in the structure of PLB (Programmable Logic Block, programmable logic module), the a1 terminal of the full adder ADD1 can input the signal m connected from the outside of the PLB, the signal n output from the front LUTx, or the constant connected 0 / 1; its b1 input terminal can input the signal k of f5 from the outside of the PLB, the signal p of the xy output of the front LUT, or acces...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com