Subunit array splicing pretreatment method of very large scale integrated circuit layout hierarchy comparison tool

A technology of integrated circuits and subunits, which is applied in the field of layout subunit array splicing and preprocessing, can solve the problems of decreased efficiency of layout level comparison tools, and achieve the effects of speeding up layout comparison, eliminating level differences and saving memory.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

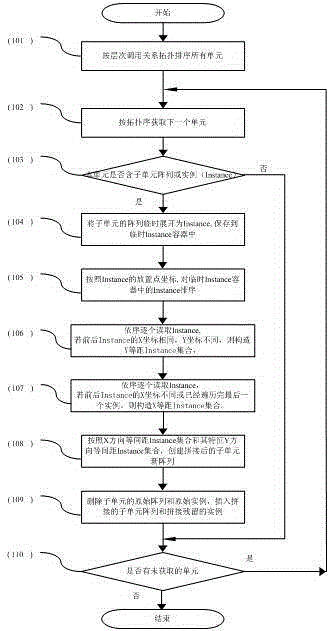

[0025] as attached figure 1 Shown, the concrete realization process of the present invention is as follows:

[0026] Ø Step (101), call all units according to the hierarchical relationship, sort topologically, and go to step (102).

[0027] Ø Step (102), according to the topological sequence, take out the next unprocessed unit, go to step (103).

[0028] Ø Step (103), judging whether the current unit contains subunit arrays or instances, if so, go to step (104), otherwise the current unit does not operate, and directly goes to step (110).

[0029] Ø Step (104), temporarily expand the array of subunits into Instance, save it in the temporary Instance container, and go to step (105).

[0030] Ø Step (105), sort the Instances in the temporary Instance container according to the placement point coordinates of the Instances, and go to step (106). The method of Instance topological sorting is as follows: according to the coordinates of the Instance placement points, they are firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com